## SI-C671xDSP-PMC

# TMS320C671x DSP Board for PMC Bus

## **Key Features**

- 1800 MFLOPS peak performance with C6713, 32 bit floating/fixed point precision.

- Up to 256MB SDRAM, using conventional PC133 SDRAM SO-DIMM format.

- Full 32 bit bi-directional PCI initiated bus mastering, with 132MB/sec peak transfer rate.

- Memory mapped host communications port.

- Software development tools from Sheldon Instruments includes <u>QuVIEW</u>, <u>QuBASE</u> and the SI-DDKs; as well compatibility with separately purchased TI and third party tools.

- Windows and Linux drivers and sample application support.

- Expansion connectors for prototyping, analog & digital I/O daughtercards.

- JTAG port for in system development and debugging.

#### Introduction

The SI-C6xDSP-PMC from Sheldon Instruments is a powerful Digital Signal Processor (DSP) card for your PC equipped with a 32 bit PCI bus. It is based on Texas Instruments' 225-300Mhz TMS320C6713, 32 bit DSP, and can transform your PC into an ultra high performance development system and DSP accelerator. A full line of software development tools are available from Sheldon Instruments and TI, which include compilers, assemblers, linkers, and debuggers.

#### Host PCI bus to DSP Link

The hardware interface between the host PCI bus and the DSP is implemented with PLX's PCI9054 device. Onboard control logic arbitrates the appropriate timing between the C6x's EMIF bus, the boot SRAM/Flash, and the PCI9056's local bus. A combination of hardware and software handshaking takes place in order to support a myriad of data transfer schemes, where the host side can be selected to operate in one mode and the DSP in another. From the host PCI side, three (3) modes are available: 1) target/slave mode, 2) PCI initiated bus mastered transfer mode with the PCI9056 acting as the bus master, and 3) bus mastering with the DSP acting as the PCI bus master. From the DSP side, three (3) modes are available: 1) standard programmed I/O, 2) asynchronous DMA, and 3) synchronous DMA.

Host target/slave mode accesses are performed when the DSP is either disabled (reset asserted) or enabled (reset deasserted). While the DSP is disabled, the host uses target/slave mode transfers to load an initialization COFF file to the card's boot SRAM/Flash memory, as well as to access expansion

daughter modules. After DSP activation, any combination of data transfer modes can be used on either side.

For most applications, the most efficient method of large data block transfer is to use PCI bus mastering, as it requires minimal host intervention. The first bus master method involves using the PCI9056's DMA engine, in conjunction with the DSP using programmed I/O or its own DMA engine. The second bus master transfer method allows the DSP to act as the PCI bus master, where it actually has direct access to the host computer's main memory!

### **Memory Options**

RUMENTS

The SI-C6xDSP-PMC is configured with conventional 144 pin SO-DIMM socket to accommodate standard, 3.3V non-buffered PC133 SDRAM modules used in laptops. The SI-C6xDSP-PMC supports \*half\* of the capacity on 64MB, 128MB, 256MB, and 512MB module sizes, making it a very cost effective solution for the most demanding and memory intensive applications.

### **Hardware Support**

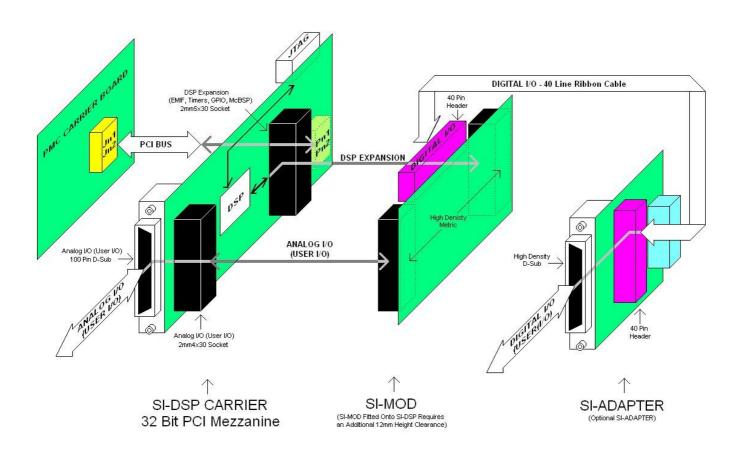

The SI-C6xDSP-PMC includes expansion connectors allowing for custom designs, or for attaching 'off the shelf' multifunction I/O modules from Sheldon Instruments. Sheldon Instruments offers several daughter modules for multichannel analog and digital I/O, including 4 to 64 channels of 16 bit ADCs and DACs.

## **Expandability Diagram**

©Copyright 2007 Sheldon Instruments Incorporated. All rights reserved. Product and company names listed are trademarks or trade names of their respective companies.

## Software Support

The SI-C6xDSP-PMC is available with extensive development tools from Sheldon Instruments and TI.

For quick turnkey development, Sheldon Instruments offers <u>QuVIEW</u> and <u>QuBASE</u>, which are a set of DSP-resident libraries for real time performance that greatly accelerate data acquisition, signal processing, and control applications. <u>QuVIEW</u> is a real time accelerator for LabVIEW, and <u>QuBASE</u> a real time accelerator for Visual Basic. A full range of examples and tutors are provided to demonstrate their ease of use and breadth of functionality and capabilities. <u>QuBASE</u> runs under Win98/2000/XP, while <u>QuVIEW</u> also runs under Linux.

When purchased as a DSP evaluation board, Sheldon Instruments also includes free sample DSP and Win98/2000/XP or Linux device driver source code to accompany TI's development environment. The DSP source code illustrates full communication modes, and the Win98/2000/XP or Linux device driver source code includes the complete SI-DDK, along with COFF file loader utilities.

## **Technical Specifications**

#### **Processor for SI-C671xDSP:**

- 225-300Mhz TMS320C6713.

- 16 DSP DMA channels, 2 PCI DMA channels.

#### **Memory:**

- SDRAM program and data memory:

- Standard 3.3V, non-buffered PC133 SO-DIMM format.

- Sizes: 64MB, 128MB, 256MB and 512MB, with x16 organizations. Only half of capacity is used.

- PC133 SDRAM module clocked from E Clock running at 75Mhz, maximum delay of memory ICs mounted on module not to exceed 7.5 nsec.

- Single bank SO-DIMMs: supports \*half\* of memory ICs mounted on single bank modules, with all capacity only mapped on CE2 (DSP memory region starting at 0xA0000000). The DSP's CE3 region is left empty (DSP memory region starting at 0xB000000).

- Dual bank SO-DIMMs: supports \*half\* of memory ICs mounted on dual bank modules, with quarter of module capacity mapped on CE2 (DSP memory region starting at 0xA0000000), and the second quarter mapped on CE3 (DSP memory region starting at 0xB000000). Remaining capacity is ignored.

- Host accessible while DSP is active, with multiple communication options.

- Boot memory:

- 512kx8 SRAM or 2Mx8 Flash memory.

- Configured as Dual Access memory: Accessible by host (only while DSP is inactive/reset) for downloading COFF files. Accessed by DSP during its boot loading process.

- Mapped on CE1 (DSP memory region starting at 0x90000000).

#### **Interface to Host:**

- PCI initiated bus master transfer speeds:

- Up to 132Mbyte/sec bursts with block sizes of eight (8) 32 bit words.

- Up to 25Mbyte/sec sustained transfers of any block size, using DMA.

- Up to seven 32 bit, bi-directional communications modes between TMS320C6x and the PCI9056:

- Host target/slave access mode, combined with DSP I/O or DSP's DMA engine.

- Block Mode DMA Bus Master mode, using the PCI9054 as the PCI bus master, combined with DSP I/O or DSP's DMA engine.

- PCI Initiated/Local Master with the DSP as the PCI bus master, with DSP I/O or DSP's DMA engine.

- The PCI9056's internal registers are tied onto the C6x's EMIF bus, mapped on CE0 (DSP memory region starting at 0x80000000).

- Four C6x routable interrupts:

- Up to three C6x interrupts can be routed for basic communication and DMA synchronization.

- Up to two C6x interrupts can be routed to expansion connectors.

#### **Peripheral Expansion:**

ELU

STRUMENTS

- Two 2mm socket connectors, and one external 68 pin half pitch DSUB connector (SCSI style):

- DSP Expansion: First external 2mm pitch, 5x30 (150 contacts) socket connector for interfacing the expansion board to the DSP's bus, or linking to all of the DSP's peripheral ports (McBSP, McASP, HPI/GPIO, Timers). Nominal 4.3V CMOS/TTL logic levels, directly tied to 74FCT2245 class of bidirectional buffers.

- User I/O: Second external 2mm pitch, 4x30 (120 contacts) socket connector for interfacing external user defined signals to custom daughter board. Linked only to externally accessible 68 pin half pitch DSUB connector.

- External 68 pin, half pitch (0.050"), Series III DSUB connector (68 pin SCSI style) for interfacing external user defined signals to the 2mm User I/O connector.

- DSP Expansion 2mm connector decodes 64Kx32 words, mapped into the DSP's EMIF bus, which contains the following signals:

- Address: A15-A0 (DWord Boundary).

- o Data: D31-D0.

- Control: X\_R/Wn, X\_CSn, X\_INT[1:0] (software routable to DSP's EXTINT[7:4]), X\_RDY, X\_CLK[1:0].

- Peripheral Ports: McBSP[1:0], HPI/GPIO, TINP[1:0], TOUT[1:0].

- Host +3.3Vdc, +5Vdc, +/-12Vdc, +1.8Vdc and GND.

• One 14 pin header for JTAG port.

#### Software:

- Win98/2000/XP and Linux driver support.

- Extensive <u>QuVIEW</u> DSP-resident libraries for LabVIEW, including examples for real time acquisition, signal processing, and control.

- Extensive <u>QuBASE</u> DSP-resident libraries for Visual Basic, including examples for real time acquisition, control and analysis.

- Sample code for COFF loaders, PC <-> DSP communications source code and SI-DDK.

- Compatible with separately purchased TI debuggers, C/C++ compilers, assemblers and linkers.

## Physical Dimensions & Electrical Requirements:

- PMC card measuring 5.86"(L) x 2.9"(H) or 149cm(L) x 74cm(H).

- 0.18lbs or 85 grams.

- Supply Voltages: 3.3V for all circuitry, and 5V for expansion bus buffers; 3V expansion buffers may be placed on special request.

- 4.5 watts (3.3V @ 1.5A) typical with 128MB SDRAM.

#### **Ordering Information:**

- SI-C6713DSP-PMC:

- SI-C6713DSP-PMC-64.

- SI-C6713DSP-PMC-128.

- SI-C6713DSP-PMC-256.

#### **Contact Information**

Sheldon Instruments 10393 San Diego Mission Road - Suite 202 San Diego, CA 92108-2176 USA Tel (619) 282-6700 Fax (619) 282-6710 Email info@sheldoninst.com Web www.sheldoninst.com

©Copyright 2007 Sheldon Instruments Incorporated. All rights reserved. Product and company names listed are trademarks or trade names of their respective companies.