## **GP1020** SIX-CHANNEL PARALLEL CORRELATOR CIRCUIT FOR GPS OR GLONASS RECEIVERS

The GP1020 is a six-channel CMOS digital correlator which has been designed to work with the GP1010 L1-channel down-converter or other integrated circuits, and may be used to acquire and track the GPS C/A code or the GLONASS signals.

For each of the six channels the GP1020 includes independent digital down-conversion to baseband, C/A code generation, correlation, and accumulate-and-dump registers.

The GP1020 interfaces with a microprocessor via a 16-bit data bus to control the acquisition and tracking processes using the various registers on the chip.

#### **FEATURES**

- Six Fully Independent Correlation Channels

- Switchable to Receive GPS or GLONASS Codes

- Input Multiplexer for Multiple GPS Front-Ends Allows Antenna Diversity

- Input Multiplexer for GLONASS Multiple (Separate Channels) Front-Ends

- Digital Interface Compatible with Most 16 or 32-Bit Microprocessors

- Fully Compatible with GP1010 GPS Receiver Front-End

- Sideways Stackable to give Multiples of Six Channels

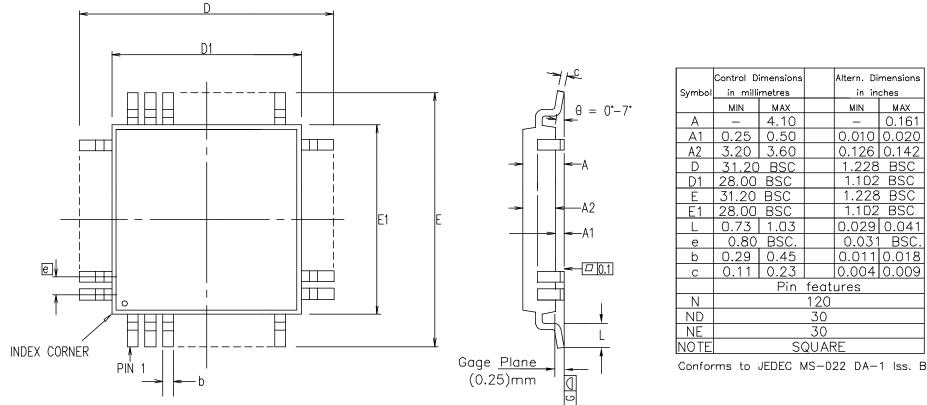

- 120-pin Plastic Quad Flatpack

- Power Dissipation Less Than 500mW

## **APPLICATIONS**

- GPS or GLONASS Navigation Systems

- High Integrity Combined Receivers

- GPS Geodetic Receivers

- GPS Time Reference

## **ORDERING INFORMATION**

The GP1020 is available in 120-pin Quad Flatpacks (Gullwing formed leads) in both Commercial (0°C to +70°C) and Industrial (-40°C to +85°C) grades. The ordering codes below are for standard screened devices.

#### **ORDERING CODES**

GP1020 CG GPKR Commercial - Plastic 120-pin QFP (GP120) GP1020 IG GPKR Industrial - Plastic 120-pin QFP (GP120)

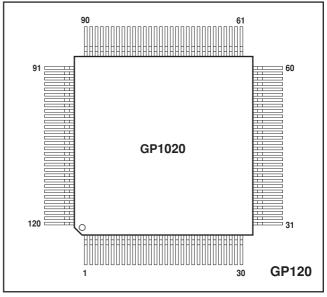

Fig 1 Pin connections - top view

#### **ABSOLUTE MAXIMUM RATINGS**

These are not the operating conditions, but are the absolute limits which if exceeded, even momentarily, may cause permanent damage. To ensure sustained correct operation the device should be used within the limits given under Electrical Characteristics.

| Supply voltage (V <sub>DD</sub> ) from ground | ( $V_{SS}$ ): -0.3V to+6.0 V      |

|-----------------------------------------------|-----------------------------------|

| Input voltage (any input pin):                | $V_{SS}$ -0.3V to $V_{DD}$ +0.3 V |

| Output voltage (any output pin):              | $V_{SS}$ -0·3V to $V_{DD}$ +0·3 V |

| Storage temperature:                          | -55°C to +125°C                   |

#### **RELATED PRODUCTS**

| Part   | Description            | Datasheet<br>Reference |

|--------|------------------------|------------------------|

| DW9255 | 35·42MHz SAW Filter    | DS3861                 |

| GP1010 | GPS Receiver Front-End | DS3076                 |

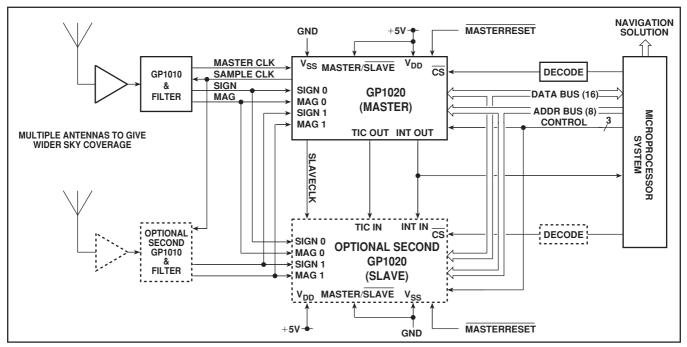

## **TYPICAL GPS RECEIVER (Fig. 2)**

All satellites use the same L1 frequency of 1575·42MHz, but different Gold codes, so a single front-end may be used. To achieve better sky coverage it may be desirable to use more than one antenna, in which case separate front-ends will be needed.

Fig. 2 GPS receiver simplified block diagram

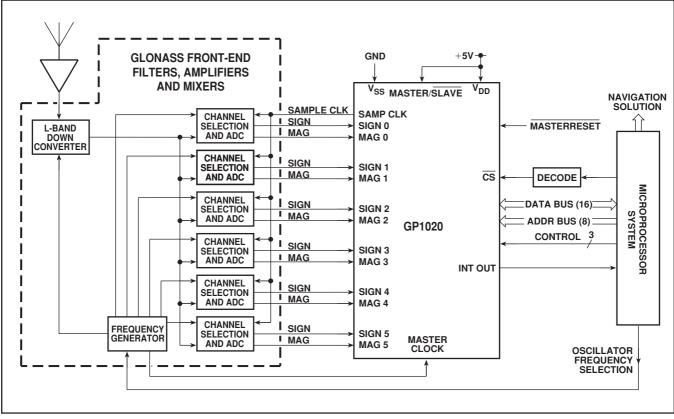

## **TYPICAL GLONASS RECEIVER (Fig. 3)**

Each satellite will use a different 'L1' carrier frequency, in the range 1602·5625 to 1615·500MHz, with 0·5625MHz spacing, but all with the same 511-bit spreading code. The normal method for receiving these signals is to use several front-ends, perhaps with the first LNA and mixer common, but certainly with different final local oscillators and mixers.

Fig. 3 GLONASS receiver simplified block diagram

## PIN DESCRIPTIONS (See Application Notes, p. 41)

All  $V_{SS}$  and all  $V_{DD}$  pins must be used in order to ensure reliable operation. Several pins, such as Satellite Inputs 2 to 9 Sign and Magnitudes are also used for device testing, but only as a secondary function.

| Pin<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Signal<br>name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A7<br>A8<br>MASTER/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br>                            | Register Address, bit 7<br>Register Address, bit 8<br>Master or slave mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>5<br>6<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SLAVE<br>TSCAN<br>TCKS<br>TDI1<br><u>MASTER</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | Scan Test mode select<br>Test Clock select<br>Serial Test Data Input<br>Master Reset (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>9<br>21<br>22<br>23<br>24<br>26<br>27<br>28<br>9<br>30<br>12<br>33<br>34<br>56<br>37<br>8<br>9<br>41<br>34<br>45<br>36<br>37<br>8<br>9<br>41<br>12<br>13<br>14<br>5<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>26<br>27<br>28<br>29<br>30<br>13<br>23<br>34<br>35<br>36<br>37<br>8<br>9<br>4<br>12<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>13<br>23<br>34<br>35<br>36<br>37<br>8<br>9<br>4<br>12<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>13<br>23<br>34<br>35<br>36<br>37<br>8<br>9<br>4<br>1<br>1<br>1<br>1<br>8<br>1<br>8<br>9<br>8<br>9<br>1<br>1<br>1<br>1<br>1<br>1<br>8<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | MASTER<br>RESET<br>MOT/INTEL<br>CS<br>Vss<br>VDD<br>WEN<br>RW<br>TMS2<br>TMS1<br>TMAG<br>TSIGN<br>MAG2<br>100/219kHz<br>VDD<br>Vss<br>INTOUT<br>SIGN2<br>MAG3<br>SIGN3<br>MAG4<br>SIGN4<br>MAG5<br>SIGN4<br>MAG5<br>SIGN5<br>MAG6<br>SIGN6<br>MAG7<br>SIGN7<br>MAG8<br>SIGN7<br>MAG8<br>SIGN7<br>MAG8<br>SIGN8<br>MAG9<br>SIGN9<br>MAG1<br>SIGN1<br>Vss<br>VDD<br>VSS<br>VDD<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD<br>VSS<br>VDD | +                               | Master Reset (active low)<br>Motorola (hi) or Intel (lo) bus select<br>Chip Select (active low) for bus<br>Ground<br>Positive supply<br>Bus control - see note 1<br>Bus control - see note 1<br>Test Mode Select 2<br>Test Mode Select 1<br>Test PRN Pattern Magnitude o/p<br>Test PRN Pattern Sign output<br>Satellite Input 2, Magnitude<br>Programmable Interrupt Timer clock<br>Positive supply<br>Ground<br>Interrupt out to microprocessor<br>Satellite Input 2, Sign<br>Satellite Input 3, Magnitude<br>Satellite Input 4, Magnitude<br>Satellite Input 5, Sign<br>Satellite Input 5, Sign<br>Satellite Input 6, Magnitude<br>Satellite Input 7, Magnitude<br>Satellite Input 7, Sign<br>Satellite Input 8, Sign<br>Satellite Input 9, Magnitude<br>Satellite Input 9, Magnitude<br>Satellite Input 9, Sign<br>Satellite Input 9, Sign<br>Satellite Input 9, Sign<br>Satellite Input 9, Sign<br>Satellite Input 1, Magnitude<br>Satellite Input 1, Magnitude<br>Satellite Input 1, Sign<br>Satellite Input 1, Sign |

| 41<br>42<br>43<br>44<br>45<br>46<br>47<br>48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\begin{array}{c} v_{DD} \\ MAG0 \\ SIGN0 \\ SAMPCLK \\ V_{DD} \\ MASTERCLK \\ V_{SS} \\ Bias \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | +<br>-<br>-<br>0<br>+<br>-<br>0 | Satellite Input 0, Magnitude<br>Satellite Input 0, Sign<br>Sampling clock to down-converter<br>Positive supply<br>40MHz Master Clock<br>Ground<br>Bias for MASTERCLK in 600mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\begin{array}{r} 49\\ 50\\ 51\\ 52\\ 53\\ 54\\ 55\\ 56\\ 57\\ 58\\ 59\\ 60\\ 61\\ 62\\ 63\\ 64\\ 65\end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\begin{array}{c} V_{SS}\\ V_{DD}\\ V_{SS}\\ CLKSEL\\ PLLLOCKIN\\ BITECNTL\\ GLONASSBIT\\ SLAVECLK\\ INTIN\\ TCK1\\ TCK2\\ TCK3\\ TCK4\\ TCK5\\ TCK6\\ TCK6\\ TCK7\\ TCK8\\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - +                             | AC-coupled mode<br>Ground<br>Positive supply<br>Ground<br>Sets 100/219kHz to 100or 219kHz<br>PLL lock status from down-converter<br>BITE control to down-converter<br>I/P to monitor GLONASS front-end<br>20MHz clock from Master to slave<br>Interrupt to slave to sync to Master<br>Test Clock 1<br>Test Clock 2<br>Test Clock 3<br>Test Clock 4<br>Test Clock 4<br>Test Clock 5<br>Test Clock 6<br>Test Clock 7<br>Test Clock 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin<br>No.                                                                                                                                                                                                                                                                                                                                                    | Signal<br>name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Туре                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} 66\\ 67\\ 68\\ 69\\ 70\\ 71\\ 72\\ 73\\ 74\\ 75\\ 76\\ 77\\ 78\\ 79\\ 80\\ 81\\ 82\\ 83\\ 84\\ 85\\ 86\\ 87\\ 88\\ 90\\ 91\\ 92\\ 93\\ 94\\ 95\\ 96\\ 97\\ 98\\ 99\\ 100\\ 101\\ 102\\ 103\\ 104\\ 105\\ 106\\ 107\\ 108\\ 109\\ 110\\ 111\\ 112\\ 113\\ 114\\ 115\\ 116\\ 117\\ 118\\ 119\\ 120\\ 120\\ 120\\ 120\\ 120\\ 120\\ 120\\ 120$ | TICIN<br>TICOUT<br>D0<br>D1<br>$V_{SS}$<br>$V_{DD}$<br>D2<br>D3<br>TIME MARK<br><u>RTCINT</u><br>MARKFB1<br>MARKFB2<br>D4<br>D5<br>$V_{DD}$<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D6<br>D7<br>$V_{SS}$<br>D7<br>$V_{SS}$<br>D0<br>TCK<br>TRST<br>NANDOP<br>TMS<br>TDI<br>MARKFB3<br>TDO7<br>DISCOP<br>TDO6<br>TDO5<br>D8<br>D9<br>$V_{SS}$<br>$V_{DD}$<br>D10<br>D11<br>TDO5<br>D8<br>D9<br>$V_{SS}$<br>D10<br>D10<br>D11<br>TDO3<br>TDO2<br>TDO1<br>D12<br>D13<br>$V_{DD}$<br>$V_{SS}$<br>D14<br>D15<br>ALE<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6 | -000000000000000000000000000000000000 | TIC input to slave<br>TIC output from Master<br>Data Bus, bit 0<br>Data Bus, bit 1<br>Ground<br>Positive supply<br>Data Bus, bit 2<br>Data Bus, bit 3<br>One pulse per second output<br>Real time clock interrupt input<br>Timemark line driver feedback<br>Data Bus, bit 4<br>Data Bus, bit 5<br>Positive supply<br>Ground<br>Data Bus, bit 6<br>Data Bus, bit 7<br>Bus timing mode - see note 2<br>Test Structure - see note 3<br>Boundary Scan output<br>Boundary Scan clock<br>Boundary Scan clock<br>Boundary Scan control<br>Boundary Scan control<br>Boundary Scan input<br>Timemark line driver feedback<br>Serial Test Data Output 7<br>On/Off control for LNA by GP1010<br>Serial Test Data Output 5<br>Data Bus, bit 10<br>Data Bus, bit 11<br>Serial Test Data Output 4<br>Serial Test Data Output 4<br>Serial Test Data Output 3<br>Serial Test Data Output 4<br>Serial Test Data Output 3<br>Serial Test Data Output 4<br>Serial Test Data Output 4<br>Serial Test Data Output 2<br>Serial Test Data Output 3<br>Serial Test Data Output 4<br>Serial Test Data Output 3<br>Serial Test Data Output 4<br>Serial Test Data Output 2<br>Serial Test Data Output 3<br>Serial Test Data Output 4<br>Serial Test Data Output 2<br>Serial Test Data Output 2<br>Serial Test Data Output 3<br>Serial Test Data Output 2<br>Serial Test Data Output 3<br>Serial Test Data Output 4<br>Serial Test Data Output 5<br>Data Bus, bit 12<br>Data Bus, bit 13<br>Positive supply<br>Ground<br>Data Bus, bit 14<br>Data Bus, bit 15<br>Address Latch Enable,<br>bus control<br>Register Address, bit 2<br>Register Address, bit 3<br>Register Address, bit 5<br>Register Address, bit 6 |

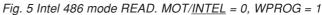

**NOTE 1.** The functions of <u>RW</u> and WEN pins depend on whether the GP1020 is in Motorola<sup>TM</sup> (MOT/<u>INTEL</u> = '1') or Intel<sup>TM</sup> mode (MOT/<u>INTEL</u> = '0'). In Motorola mode, WEN is an enable (active high) and <u>RW</u> is Read/ Write select ('1' = Read). In Intel mode <u>RW</u> is Read, active low, and WEN is Write, also active low.

| MOT/INTEL | Mode     | WEN | RW | Function |

|-----------|----------|-----|----|----------|

| 1         | Motorola | 1   | 0  | Write    |

| 1         | Motorola | 1   | 1  | Read     |

| 0         | Intel    | 1   | 0  | Read     |

| 0         | Intel    | 0   | 1  | Write    |

**NOTE 2.** WPROG is used to modify the timing of bus operations; when it is held HIGH the internal write signal is ORed with ALE to allow time for the internal address lines to stabilise; when it is held LOW there is no delay added to write. **NOTE 3.** NANDOP (pin 90) is the output of a spare gate with inputs on NANDA (pin 85) and NANDB (pin 86).

## **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions (unless otherwise stated): Supply voltage,  $V_{DD} = 5V \pm 10\%$ ; Ambient Temperature,  $T_{AMB} = 0$ °C to +70°C (CG grade),-40°C to +85°C (IG grade). **DC CHARACTERISTICS**

| Characteristic                                                                                                                                                               |                          | Value                       |                           |                    | Conditions                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------|---------------------------|--------------------|-----------------------------------------------------------------------------------------------------|

| Gharacteristic                                                                                                                                                               | Min.                     | Тур.                        | Max.                      | Units              | Conditions                                                                                          |

| Supply current, I <sub>DD</sub> , chip fully active                                                                                                                          |                          |                             | 100                       | mA                 |                                                                                                     |

| CMOS inputs with pullup resistors to V <sub>DD</sub> : <u>RTCINT,</u><br>MASTER/ <u>SLAVE,</u> MARKFB (3:1), NANDA, NANDB,<br>WPROG, ALE                                     |                          |                             |                           |                    |                                                                                                     |

| Input voltage high<br>Input voltage low<br>Bullup register                                                                                                                   | 0·8V <sub>DD</sub><br>20 | 75                          | 0.2V <sub>DD</sub>        |                    |                                                                                                     |

| Pullup resistor<br>CMOS inputs with pulldown resistors to V <sub>SS</sub> : MOT/ <u>INTEL</u> ,<br>CLKSEL, INT IN, TIC IN                                                    | -                        | 75                          | 250                       | kΩ                 |                                                                                                     |

| Input voltage high<br>Input voltage low<br>Pulldown resistor                                                                                                                 | 0.8V <sub>DD</sub><br>20 | 75                          | 0·2V <sub>DD</sub><br>250 | V<br>V<br>kΩ       |                                                                                                     |

| CMOS inputs without either pullup or pulldown resistors:<br><u>MASTERRESET, CS,</u> WEN, <u>RW</u> , MASTERCLK (note 1),<br>SLAVECLK, A (8:1), D (15:0), TCK, TDI, TMS, TRST |                          |                             | 230                       | 122                |                                                                                                     |

| Input voltage high<br>Input voltage low<br>Input leakage current                                                                                                             | 0∙8V <sub>DD</sub>       | 1                           | 0·2V <sub>DD</sub><br>10  | V<br>V<br>μA       | V <sub>SS</sub> <v<sub>PIN<v<sub>DD</v<sub></v<sub>                                                 |

| TTL inputs with pullup resistors to V <sub>DD</sub> : SIGN (9:0),<br>MAG (9:0), PLLLOCKIN, GLONASSBIT<br>Input voltage high                                                  | 2.0                      |                             | 0.0                       | VV                 |                                                                                                     |

| Input voltage low<br>Pullup resistor<br>TTL inputs with pulldown resistors to V <sub>ss</sub> : TSCAN, TCKS,                                                                 | 20                       | 75                          | 0·8<br>250                | ν<br>kΩ            |                                                                                                     |

| TDI1, TMS1, TMS2<br>Input voltage high<br>Input voltage low                                                                                                                  | 2.0                      |                             | 0.8                       | V<br>V             |                                                                                                     |

| Pulldown resistor<br>Input for low level clocks: MASTERCLK (note 1)<br>Peak to peak sinewave                                                                                 | 20<br>600                | 75                          | 250                       | kΩ<br>mV           | AC coupled                                                                                          |

| Power level 1 outputs: TMAG, TSIGN, TDO, TDO (7:1),<br>NANDOP                                                                                                                |                          |                             |                           |                    |                                                                                                     |

| Output voltage high<br>Output voltage low<br>Power level 3 outputs: 100/219kHz, INT OUT, SAMPCLK,                                                                            | V <sub>DD</sub> -1       | V <sub>DD</sub> -0·5<br>0·2 | 0.4                       | V<br>V             | $I_{OH} = -1.5mA$<br>$I_{OL} = 1.5mA$                                                               |

| TIC OUT, BITE CNTL, DISCOP, TIMEMARK<br>Output voltage high<br>Output voltage low                                                                                            | V <sub>DD</sub> -1       | V <sub>DD</sub> -0·5<br>0·2 | 0.4                       | V<br>V             | $I_{OH} = -4.5mA$<br>$I_{OL} = 4.5mA$                                                               |

| Power level 1 outputs with tri-state: MAG (9:2), SIGN (8:2),<br>TCK (7:1)<br>Output voltage high<br>Output voltage low                                                       | V <sub>DD</sub> -1       | V <sub>DD</sub> -0·5<br>0·2 | 0.4                       | V<br>V             | $I_{OH} = -1.5mA$<br>$I_{OL} = 1.5mA$                                                               |

| Output leakage current<br>Power level 3 output with tri-state: SLAVECLK<br>Output voltage high<br>Output voltage low                                                         | V <sub>DD</sub> -1       | V <sub>DD</sub> -0·5<br>0·2 | 10<br>0·4<br>10           | μA<br>V<br>V       | $V_{SS} < V_{PIN} < V_{DD}$ $I_{OH} = -4.5mA$ $I_{OL} = 4.5mA$ $V_{SS} < V_{PIN} < V_{DD}$          |

| Output leakage current<br>Power level 6 output with tri-state: D (15:0)<br>Output voltage high<br>Output voltage low<br>Output leakage current                               | V <sub>DD</sub> -1       | V <sub>DD</sub> -0·5<br>0·2 |                           | μΑ<br>V<br>V<br>μΑ | $V_{SS} < V_{PIN} < V_{DD}$<br>$I_{OH} = -9.0mA$<br>$I_{OL} = 9.0mA$<br>$V_{SS} < V_{PIN} < V_{DD}$ |

| Bias output: BIAS                                                                                                                                                            | Special o                | utput to be                 | used only                 | ı<br>as showı      | I<br>n in Fig. 12 (page 8                                                                           |

NOTE 1. The input MASTERCLK may be driven by either CMOS logic levels or by a low amplitude sinewave if the BIAS pin is connected as shown in Fig. 12.

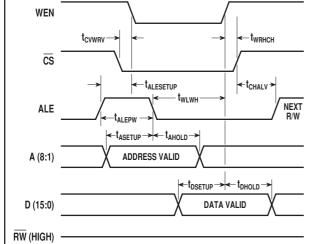

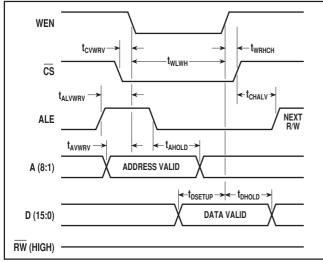

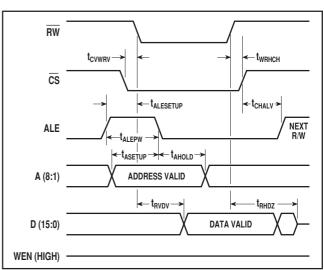

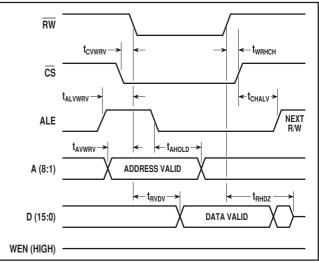

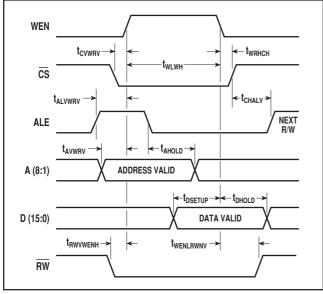

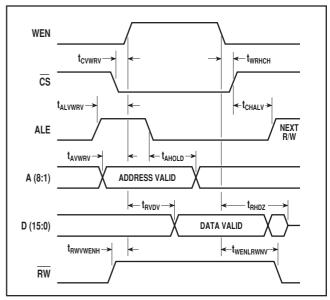

## TIMING CHARACTERISTICS (See Figs. 4 to 9)

| Characteristic                                         | Symbol                | Val  | ue   | Units | Conditions |

|--------------------------------------------------------|-----------------------|------|------|-------|------------|

| Gharacteristic                                         | Symbol                | Min. | Max. | Onits | Conditions |

| Address hold time                                      | t <sub>AHOLD</sub>    | 10   |      | ns    |            |

| ALE pulse width                                        | t <sub>ALEPW</sub>    | 20   |      | ns    |            |

| ALE valid to WEN or $\underline{RW}$ valid (WPROG = 1) | t <sub>ALESETUP</sub> | 5    |      | ns    |            |

| ALE valid to WEN or $\underline{RW}$ valid (WPROG = 0) | t <sub>ALVWRV</sub>   | 20   |      | ns    |            |

| Address valid to ALE low                               | t <sub>ASETUP</sub>   | 20   |      | ns    |            |

| Address valid to WEN or <u>RW</u> valid                | t <sub>AVWRV</sub>    | 20   |      | ns    |            |

| CS high to ALE valid                                   | t <sub>CHALV</sub>    | 10   |      | ns    |            |

| <u>CS</u> low to WEN or <u>RW</u> valid                | t <sub>CVWRV</sub>    | 0    |      | ns    |            |

| Data hold time                                         | t <sub>DHOLD</sub>    | 10   |      | ns    |            |

| Data setup time                                        | t <sub>DSETUP</sub>   | 30   |      | ns    |            |

| <u>RW</u> high to data at high impedance               | t <sub>RHDZ</sub>     | 10   | 25   | ns    |            |

| <u>RW</u> valid to data valid                          | t <sub>RVDV</sub>     | 10   | 50   | ns    |            |

| <u>RW</u> valid to WEN high                            | t <sub>RWVWENH</sub>  | 15   |      | ns    |            |

| WEN low to <u>RW</u> not valid                         | t <sub>WENLRWNV</sub> | 15   |      | ns    |            |

| Write pulse width                                      | t <sub>WLWH</sub>     | 30   |      | ns    |            |

| CS hold time after RW or WEN not valid                 | t <sub>WRCH</sub>     | 0    |      | ns    |            |

NOTE. This timing information is based on simulations and is not verified by measurement on each device.

Fig. 4 Intel 486 mode WRITE. MOT/<u>INTEL</u> = 0, WPROG = 1 (Write inhibited until ALE falling edge)

Fig. 6 Intel 186 mode WRITE. MOT/<u>INTEL</u> = 0, WPROG = 0

Fig. 7 Intel 186 mode READ. MOT/<u>INTEL</u> = 0, WPROG = 0

## **GP1020 BUS TIMING DIAGRAMS (continued)**

Fig. 8 Motorola 68xxx mode WRITE. MOT/<u>INTEL</u> = 1, WPROG = 0

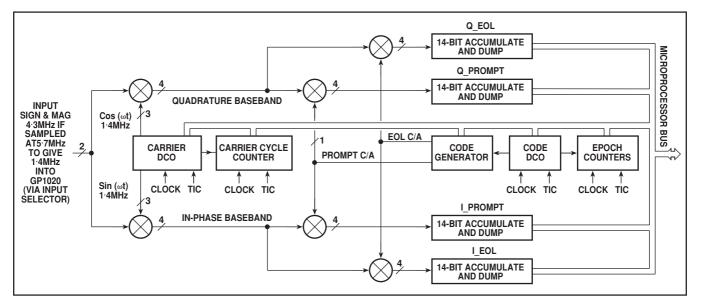

## SIGNAL PROCESSING OVERVIEW

Each channel of the GP1020 is fed with a 2-bit (or optionally with a 1-bit) GPS digital IF at around 1.4MHz, from the input multiplexer that connects one of ten signal sources to the channel input. This signal is first brought to baseband using an on-chip digital mixer driven by a programmable digital local oscillator. It is then correlated with a C/A code internally generated by a programmable Gold code generator; the correlation result is the sum of the comparisons of individual code chips over a complete code period (an 'epoch' in GPS terminology). A large positive or a large negative sum indicate good correlation but with opposite modulation, where the size of 'large' will depend on the current signal to noise ratio, while a small sum indicates poor correlation and the need to adjust the loops or choose another satellite.

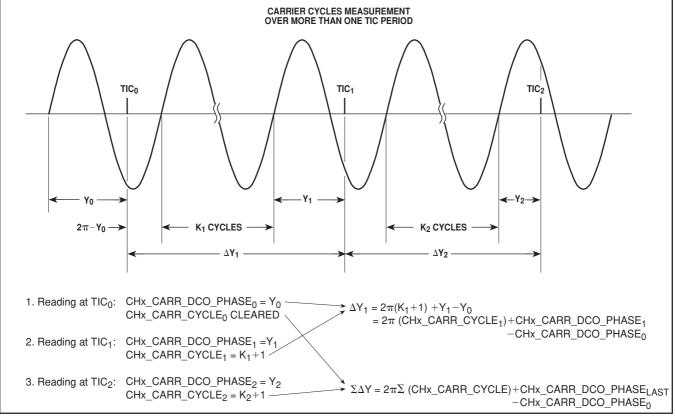

These results form the 'Accumulated Data' and are made available to the microprocessor to both control the tracking loops and to give the broadcast satellite data, the 'Navigation Message' when demodulated. Periodically, the code epoch count, the code phase, and the carrier phase of all channels, are sampled at the same instant to form the 'Measurement Data' and are also made available to the processor.

## **DESCRIPTION OF BLOCKS (see Fig. 10)**

#### **CLOCK GENERATOR**

The Clock Generator block generates the various clocks required in the GP1020, which can be operated either as a master or as a slave device. When it is operated as a master, the Clock Generator block is driven by a 40MHz clock provided by the accompanying front-end chip, the GP1010, and to drive the slaves a 20MHz output SLAVE CLK is provided. When the GP1020 is operated as a slave, it is driven only by this 20MHz SLAVE CLK from the master device. In the master the 40MHz is divided in a counter to form seven clock phases to control the data flow, but to get the same timing in the slaves twin 20MHz dividers use both high and low phases separately to give the effect of 40MHz clocking.

When in master mode these seven phases are also used to generate a sampling clock (SAMP CLK) output at 40MHz÷7 = 5·71MHz, which drives the data sampling clock input of the GP1010. A 100/219kHz output is provided for use as a micro-processor Programmable Interrupt Clock.

Fig. 9 Motorola 68xxx mode READ. MOT/<u>INTEL</u> = 1, WPROG = 0

#### TIMEBASE GENERATOR

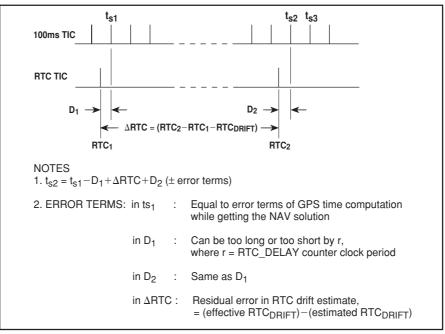

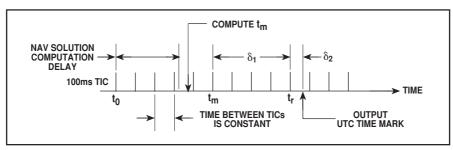

The Time Base Generator produces, among other signals: a 505.05  $\mu$ s free-running interrupt timebase INT OUT, a freerunning TIC OUT signal with a period which may be selected to be either 100ms or 9.09ms (approximately), and a TIME MARK signal with a 1 second period as an output which may be locked to GPS time, UTC, or the receiver timebase by programming its delay relative to the TIC, based on recent navigation solutions. The TIC is mainly used to latch measurement data (epoch count, code phase, code DCO phase and integrated carrier phase ( = DCO phase and cycle count)) of all six channels at the same instant.

#### **BITE INTERFACE**

The Bite Interface block contains a register which allows control over the built-in-test functions of the chip. In addition, this register allows the processor to read the state of discrete input pins, such as PLLLOCKIN connected to the status output of the GP1010, and also to set the state of the BITE CNTL and the DISCOP output pins. These can in turn, for example, be used to drive the GP1010 BITE input pin and the LNA power on/off select, respectively.

#### STATUS REGISTERS

The Status Registers block contains registers describing the status of accumulated and measurement data provided by each channel.

#### SIGNAL SELECTION BLOCK

The Signal Selection block contains a multiplexer which can be programmed to direct any of the ten input sources to any of the six tracking channels. This is needed in GLONASS where frequency division multiplexing is used and separate local oscillators are needed to receive each satellite, leading to separate IF filter channels. An input selector may be desirable in GPS, which uses code division multiplexing, to allow the use of multiple antennae to overcome problems of incomplete sky visibility.

For SIGN inputs, LOW = -, HIGH = +; for MAG inputs, LOW = 1, HIGH = 3.

#### TRACKING MODULE BLOCKS

The six Tracking Module blocks are all identical so that the term CHx is used in the description to mean any of CH1, CH2,

Fig. 10 Simplified overall block diagram

CH3, CH4, CH5 or CH6 inputs or registers. They have the architecture shown in Fig. 11. The individual sub-blocks are as follows:

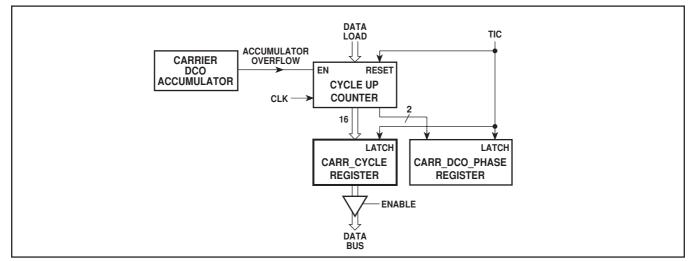

#### **CARRIER DCO**

The Carrier DCO is an accumulator performing additions at a constant rate and with a programmable increment value. It is used to synthesise the digital local oscillator signal required to bring the input signal to baseband in the mixer block, and must be adjusted away from nominal to allow for Doppler shift and crystal frequency error. The nominal frequency of the output is 1.405396825 MHz, set by loading the 26 bit CHx\_CARR\_INCR register to 01F7B1B9<sub>H</sub> and is programmed with a resolution of 42.57475 milliHertz. The very fine resolution is needed to keep the DCO in phase with the satellite signal.

#### CODE DCO

This block is a similar structure to the Carrier DCO block and is used to synthesise the oscillator signal required to drive the code generator at the proper chipping rate and phase. The nominal frequency of the output is 2.046MHz, to give a chip rate of 1.023MHz, and is set by loading the 25 bit CHx\_CODE\_INCR register to 016EA4A8<sub>H</sub> and is programmed with a resolution of 85.14949 milliHertz. Again,the very fine resolution is needed to keep the DCO in phase with the satellite signal.

#### **CODE GENERATOR**

This generates the processor-selected GPS Gold code (one of PRN code numbers 1 to 32 for normal satellites or 33 to 37 for ground based use) or the GLONASS code (fixed for all satellites) or one of eight INMARSAT codes. Twin generators are used to produce both a prompt (on-time) pattern and an early, late, or early-minus-late version for tracking use. At the end of each code sequence a signal DUMP is generated to latch the Accumulated Data, separately for each channel.

#### MIXER AND CORRELATOR

The Mixer and Correlator first mixes the digitised input signal with the Carrier DCO digital local oscillator to generate a signal at baseband, and then uses the Code Generator outputs to correlate the data stream. The block includes in-phase and phase-quadrature channels, as well as prompt and dithered (or early/late) correlator arms.

The term dither is used in the GP1020 to mean a code channel in which the timing alternates one half-chip either before or after the prompt channel, and not the now obsolete technique of Taudither, in which the prompt arm timing is oscillated a little each side of nominal to give tracking with only one arm.

#### QUADRUPLE INTEGRATE AND DUMP

The bit-by-bit results from the correlator are passed to the Quadruple Integrate And Dump block, which integrates the correlation result of individual code chips from all four correlators (in-phase and phase-quadrature, prompt and dithered arms) over a complete code period. Through the Accumulated Data registers, the processor has access to each integration result.

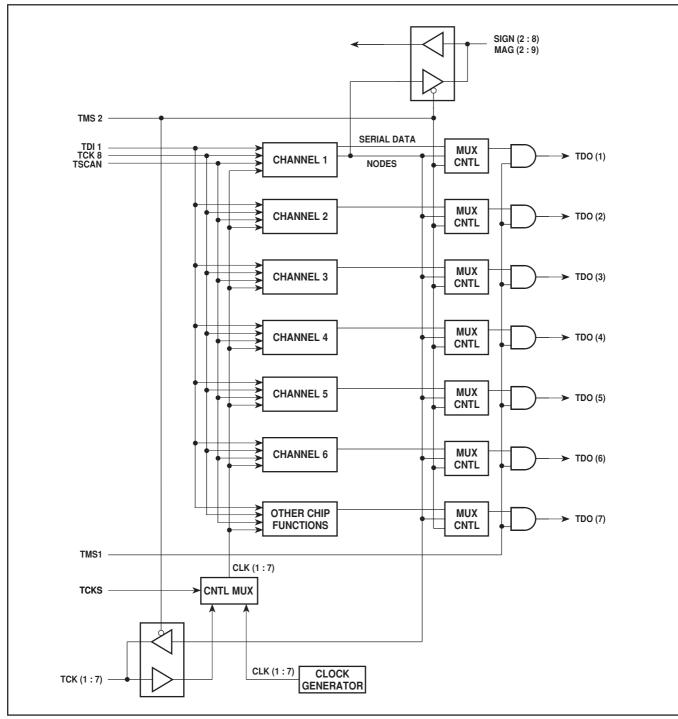

#### NAVIGATION OR TIME REFERENCE RECEIVER HARDWARE SYSTEM DESIGN

A receiver system can use one or more GP1020s. When only one is used, that IC is operated in master mode, and when more than one are used, one of them is designated as being the *master* and all of the others are operated as *slaves*. In all cases, the master chip is the one which will receive the 40MHz MASTER CLK from the GP1010 and generate, upon release of the <u>MASTERRESET</u> signal, a gated 20MHz clock which drives all slaves (if any) and allows a synchronised start-up. The master device also generates the SAMP CLK signal which drives all of the GP1010 front-ends.

The operating mode is programmed by tying the MASTER/ <u>SLAVE</u> pin to V<sub>DD</sub> for master or to V<sub>SS</sub> for slave operation. The operating mode sets the functions of MASTER CLK, SLAVE CLK and SAMP CLK pins.

The TIME MARK signal is generated by the master GP1020; the slave TIME MARK generator, although not disabled, is not synchronised with the master. The TIC signal is generated by the master and routed to the slaves to ensure a common measurement data sampling instant for all the tracking channels. The slave TIC OUT signal is not disabled but is not used.

The master INT OUT drives the slaves' INT IN pins to provide latching of status bits at a common instant. Optionally, the slave TIC OUT and INT OUT pins could be connected to the master TIC IN and INT IN pins, respectively, for testing purposes.

When more than one GP1020 is used in the same system, the devices must share a common TIC for sampling of measurement data to enable the software to calculate clock bias in the pseudoranges, and so find the correct ranges. Each GP1020 contains a state machine driven by 7 different clock phases, so for two GP1020s to share a common TIC, the devices must be synchronised. This is achieved by configuring the hardware as follows:

- All GP1020s share the same MASTERRESET signal.

- One GP1020 is designated the master chip. It is

Fig. 11 Tracking module simplified block diagram

programmed into this mode by tying the MASTER/<u>SLAVE</u> pin to  $V_{DD}$  (or by leaving it unconnected and relying on an internal pull-up resistor.)

- All other GP1020s are designated slaves and are programmed into this mode by tying their MASTER/ <u>SLAVE</u> pin to V<sub>SS</sub>.

- The master GP1020's SAMP CLK output drives all of the GP1010 front-ends. This ensures that in a multiple GP1010 application, all of the signals are being sampled at the same instant in all GP1010s. The slave GP1020s have their SAMPLING CLK output left unconnected.

- The SLAVE CLK output from the master drives the SLAVE CLK inputs on all slaves.

When the <u>MASTERRESET</u> is released, the clock generators of all devices – master and slaves – are enabled. The SLAVE CLK output of the master device will start to toggle only after the master's clock generator has reached a certain phase (200ns after the <u>MASTERRESET</u> release). The clock generator of the slave device gets reset into a state which corresponds to the next phase and starts counting as soon as the SLAVE CLK signal from the master reaches its SLAVE CLK input pin.

## IMPORTANT TIMING SIGNALS IN A TYPICAL HARDWARE DESIGN

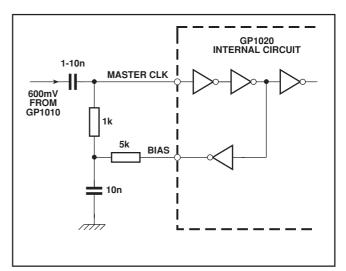

#### MASTER CLK

The MASTER CLK is a 40MHz clock which sets the timing of all functions in a GPS receiver using the GP1020. In a multiple GP1020 system only the master is given this clock and this may be connected in either of two ways, depending on the signal level. If the clock is a TTL signal it is directly connected to the MASTER CLK input and the BIAS output pin is left unconnected. The other option is an AC-coupled 600 mV peak-to-peak signal, when the BIAS output is used to set the DC voltage of the MASTER CLK pin as shown in Fig. 12. The MASTER CLK pin on each slave GP1020 is not used and should be tied to  $V_{DD}$  or  $V_{SS}$ .

#### SLAVE CLK

20MHz with 1:1 nominal mark:space ratio. Output from master GP1020, input to slave, using a bidirectional buffer controlled by MASTER/<u>SLAVE</u>. This signal is held low when the master chip is reset and starts to toggle within 200ns after <u>MASTERRESET</u> is released.

Fig. 12 Biasing circuit for master clock

#### SAMP CLK

$40MHz \div 7 = 5.7142857MHz$  output when the chip is in master mode; nominal mark:space ratio is 1:1. This signal is held low during an active <u>MASTERRESET</u> and when in slave mode. **TICOUT**

Output signal from TIC generator, used to sample measurement data and so initiate a navigation solution. TIC does not drive the microprocessor directly but sets a flag in MEAS\_STATUS\_A, which should be be examined by reading the register periodically, such as at every INT OUT.

TIC OUT is active high; active time duration is either 4.54545ms for a short TIC or 9.0909ms for a long TIC. The rising edge of TIC OUT is in advance of the effective sampling instant inside the device by 125ns. The TIC period is selectable via the TIC\_PERIOD bit of TIMER\_CNTL register to either 100ms minus 100ns (= 99.9999ms) or to 9.0909 ms.

#### TIC IN

The TIC IN input of a GP1020 is normally provided by a companion GP1020. Its use is controlled by the TIC\_SOURCE bit of the TIMER\_CNTL register and is configured in most applications so the master TIC OUT drives the slave TIC IN.

#### INT OUT

This output signal is a free running interrupt timebase which may be used to interrupt the microprocessor to initiate data transfer sufficiently often that no correlation results will be missed. The tracking loops rely on the microprocessor to adjust the DCO registers in response to signal changes so the rate of interaction must be sufficiently high. If the frequency of INT OUTis too high for the software to process then a polling scheme may be used, by inhibiting the interrupts (INT\_MASK bit in TIMER\_CNTL set low) and then periodically writing to STATUS\_LATCH and reading the status registers to check if new data is available.

The period of INT OUT is programmable; a typical value is  $505.05\mu$ s. During <u>MASTERRESET</u> the interrupt output is stopped and the pin is held LOW if in Intel mode, or HIGH if in Motorola mode. The active duration of INT OUT (HIGH for Intel, LOW for Motorola) is 252.525 $\mu$ s, which should be more than adequate to ensure that the interrupt controller in the processor will have time to respond.

#### INT IN

This input signal is normally provided by the INT OUT output of a companion GP1020; in general the master drives the slave. It is used, when selected via the INT\_SOURCE bit of the TIMER\_CNTL register, to latch the state of the status bits.

#### 100kHz/219kHz

A clock output at either 100kHz or 219kHz which may be used to drive the microprocessor interrupt timer. The frequency is set by the level on CLKSEL (HIGH for 100kHz and LOW for 219kHz).

#### MASTERRESET

When <u>MASTERRESET</u> is set LOW, all the registers, accumulators and counters are cleared, except CHX\_CNTL, which IS initialised to specific values (refer to detailed description of the registers for these values). When the device is held reset, by <u>MASTERRESET</u> set low, the following pins are driven as listed:

MASTER CLK: This input may or may not be being externallv driven during the reset. MASTERRESET internally gates MASTER CLK to ensure a well defined level on all clock lines until the release of MASTERRESET; the release of MASTERRESET must occur only when the input buffer is properly biased and the input signal is stable. SLAVE CLK: Configured as an input on slave devices and held LOW on master device.

SAMP CLK: Held LOW.

- 100/219kHz: This output is held LOW when <u>MASTER</u> <u>RESET</u> is active (also LOW) and toggles to HIGH shortly after <u>MASTERRESET</u> is released, and then runs normally.

D0-D15: High impedance.

- BITE CNTL: LOW.

- DISC OP: LOW.

- TIC OUT: LOW.

- INT OUT: This output is held LOW until interrupt inhibit is removed, when in Intel bus type mode, or is held HIGH until the inhibit is removed, when in Motorola bus type mode.

#### TIME MARK

The primary purpose of the TIME MARK output is to give a one pulse per second signal locked to UTC or GPS time. This may be followed by the correct time from the microprocessor and could be used as a reference by other navigation instruments (e.g. ARINC 743 may be wanted) or a simple reference time clock may be built.

To synchronise TIME MARK to GPS time the first stage is to acquire the measurement data at any arbitrary TIC and then calculate the full navigation solution to give the time at that TIC. From this determine a later TIC at which to acquire data again such that after the navigation solution computation delay (typically a few TIC periods long) a further delay may be programmed into DOWN\_COUNT\_HI and \_LO registers to start on the next TIC, to give TIME MARK at the required GPS whole second. This is rather a long process to get started, but once the first correct TIC choice and down counter delay are known the process can roll on with each TIC and delay calculation coming from the previous navigation solution.

To get UTC instead of GPS time it is only neccessary to read the navigation message to get the number of whole seconds difference and add this to the calculated GPS time. A possible refinement is to calculate the oscillator drift over several measurements and use this to extrapolate a better value for the delay counter. The ultimate accuracy that can be achieved is very good, but to get this the crystal must both have high stability and be drift compensated in the software; in addition, the receiver front-end delay must be known and allowed for, and the delay through the output drivers and cables must be allowed for by using the MARKFBx pins.

If, as is likely, Selective Availability is on it will be the main source of error in a well designed TIME MARK system, but better than one microsecond absolute accuracy is still possible. To reduce the effects of SA it is possible to use a stable rubidium reference oscillator and average the induced offsets over a long time to give very good peak errors of a few tens of nanoseconds.

As the main purpose of the TIME MARK output is a timing reference signal at one pulse per second for the electronic systems in an airliner, it must be both accurate and known to be accurate.

The accuracy is achieved by loading DOWN\_COUNT\_HI and \_LO with the correct offset in 50ns units from the GPS measuring TIC. As the TIC rate is nominally 1ppm less than 10Hz, the DOWN\_COUNT value should be expected to increase at around 1 $\mu$ s per one second TIME MARK, a number change of +20 each pulse. This value will need continuous fine tuning to allow for the stable and variable crystal errors.

Integrity is ensured in two ways; first, by using PROP\_DELAY to check the delay through line drivers and to verify that a TIME MARK really did occur and, secondly, by having a complex handshake sequence so that any failure in the hardware will be detected by the microprocessor. The handshake sequence is:

- Write to DOWN\_COUNT\_LO to arm the TIME MARK generator (this requires that DOWN\_COUNT\_HI is already written; as it rarely changes, this is often automatically true).

- 2. At next TIC the GP1020 will start DOWN\_COUNT.

- 3. The GP1020 will give a TIME MARK pulse output and start the PROP\_DELAY counter.

- Feed TIME MARK back through MARK\_FBx input to stop PROP\_DELAY and to set MARK\_FB\_ACK in MEAS\_STATUS\_A

- 5. Read MEAS\_STATUS\_A, normally as part of the Measurement Data transfer protocol but, on this occasion, to also clear the overwrite protection on PROP\_DELAY and to clear the MARK FB ACK bit.

- 6. Read PROP\_DELAY, once MARK\_FB\_ACK has been set (and cleared) to give a stable value for the last delay. This also re-enables the TIME MARK generator ready for a repeat of step (1) to take effect.

This may seem rather complicated, but is only needed once per second and so is little overhead if a simple system is all that is required. For a full accuracy system, the various register operations fit in with the computations needed to achieve full ARINC 743 specification.

## SATELLITE CODE SELECTION

This section describes the code selection for normal GPS and GLONASS operation; for INMARSAT codes and unusual techniques see full details in DETAILED DESCRIPTION OF REGISTERS section, under CHx\_CNTL. The same section gives details of the other bits of CHx\_CNTL.

The satellite code to be used by each channel is set by the CHx\_CNTL registers, which are addressed individually from the A8-A1 address bus by:

- 00<sub>H</sub> : Read/Write to Channel 1

- 10<sub>H</sub> : Read/Write to Channel 2

- 20<sub>H</sub> : Read/Write to Channel 3

- 30<sub>H</sub> : Read/Write to Channel 4

- $40_{H}$  : Read/Write to Channel 5  $50_{H}$  : Read/Write to Channel 6

- $70_{\rm H}$ : Write only, to all channels simultaneously

The one GLONASS code may be selected by setting bit 10 HIGH, otherwise this bit should be set LOW and bits 7 to 0 used to select one of the GPS Gold codes (see Table opposite).

## SOFTWARE REQUIREMENTS

The very wide variety of types of GPS or GLONASS receiver need to operate the correlator in different ways so, to accomodate this and also to allow dynamic adjustment of loop parameters, the GP1020 has been designed to use software for as many functions as possible. This flexibility means that the device cannot be used without a microprocessor closely linked to it, but as a processor is always needed to convert the output of the GP1020 into useful information this is not a significant limitation.

The software associated with the GP1020 can be divided into two separate modules: one to acquire and track satellite signals to give pseudoranges and another to process these to give the navigation solution and format it in a form suitable for the user. For the Navigation Solution to be possible all of the pseudoranges must have exactly the same clock error, which can then be removed iteratively to give real ranges if sufficient satellites are tracked (3 if the height is known, otherwise 4). This need for exact matching of timing errors explains the need for all of the complicated synchronisation between all channels and between master and slaves.

The following relates only to the signal processing aspects of the software, to acquire and track signals from up to six satellites per GP1020 and to obtain the pseudoranges and the navigation message. The operation of the navigation software is not dependent on the details of the correlator, and so does not need to be included in this data sheet.

An on-chip interrupt time base INT OUT is provided to help implement a data transfer protocol between the microprocessor and the GP1020 at fixed time intervals, otherwise a software based polling scheme will be needed – the choice is set by the application. If INT OUT is used, and perhaps also if polling is used, the data transfer rate is about twice the correlation result rate for each channel, so many transfers will not give new data. Bus use can be reduced by examining the status registers before each transfer to see if new data is available and then only reading the data if it useful.

It is important to note that the timing of each of the correlator channels will be locked to its own incoming signal and not to each other or to the microprocessor interrupts, so new data is generated asynchronously. The sampling instant of measurement data of all channels, however, is common to give a consistent navigation solution.

In order to acquire lock to the satellites as quickly as possible, the data from the last fix should be stored as a starting point for the next fix. It is also useful to have a real-time clock built into the receiver to give a good estimate of GPS time for the next fix; the navigation solution can be used to measure clock drift and calculate a correction for the clock to overcome ageing. The

| Bit setting<br>7654 3210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPS PRN<br>reference<br>number                                                                                                                                                         | Selected taps<br>to be EXORed<br>together            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 0001 0101<br>0010 0110<br>0011 0111<br>0100 1xx0<br>0000 1xx0<br>0001 1xx1<br>0000 0111<br>0001 011<br>0010 0011<br>0100 0011<br>0100 0101<br>0100 0101<br>0100 0101<br>0110 0111<br>0111 1xx0<br>1xx0 1xx1<br>0000 0011<br>0011 0101<br>0010 0101<br>0010 0101<br>0010 0111<br>0100 0110<br>0100 0110<br>0101 0111<br>0101 0110<br>0100 0110<br>0101 0111<br>0101 1xx0<br>0100 1111<br>0101 1xx1<br>0000 0110<br>0010 111<br>0011 1xx1<br>0001 0111<br>0001 0111<br>0011 1xx1<br>0001 0111<br>0001 0111 | $\begin{array}{c}1\\2\\3\\4\\5\\6\\7\\8\\9\\10\\11\\12\\13\\14\\15\\16\\17\\18\\19\\20\\21\\22\\23\\24\\25\\26\\27\\28\\29\\30\\31\\32\\33^*\\34^*=37\\35^*\\36^*\\37^*=34\end{array}$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

GPS Gold codes. \*Note that these codes, 33 to 37, are reserved for non-satellite use only.

user's location (or a good estimate of it) along with the Almanac and the correct time will indicate which satellites should be searched for and may be used to find an estimate of Doppler effects, while the previous clock error is the best available estimate of the present clock error. If this information is not available then the receiver must scan a much wider range of values, which will greatly increase the time to lock. The satellite Clock Correction and Ephemeris are needed for the navigation solution, so if a recent set is held in memory the calculations may begin as soon as lock is achieved and not need to wait for the retransmission (18 to 36 seconds).

This description applies to just one tracking channel but is the samd this is not necessarily the same as the other channels. The GP1020 contains four different types of registers:

- **Control Registers** which are used to program functions of the device.

- Status Registers which provide a status indication of the process taking place in the device.

- Accumulated Data Registers which provide the results of correlation with the C/A code every millisecond. This is the raw data used to acquire and track satellite signals.

- Measurement Data Registers which latch the carrier DCO phase, carrier cycle count, code DCO phase, 1 millisecond

epoch, and the 20 millisecond epoch count at every 9.09 or 100 milliseconds interval. This is the raw data used to compute pseudorange.

#### SOFTWARE SEQUENCE FOR ACQUISITION

Satellite signals seen by a GPS receiver are so weak that they are buried in the noise and can only be detected by correlation. The spectrum of each signal is spread, using 1023 chip Gold codes for GPS or a 511 chip maximal length code for GLONASS; to correlate them therefore, a locally generated code must be chosen to precisely match the spreading code type, rate, and phase. This pattern is then multiplied bit-by-bit with the incoming data stream and the results integrated over the code length to recover the signal.

The process of signal acquisition is simply the matching of receiver settings to the actual signal values. To make matters more complicated the satellite carrier frequency is shifted a little by the Doppler effect due to the motion of the satellite, the user clock will drift randomly, and (in most situations) the signal to noise ratio is poor for some satellites. As a result, the software must be 'wide-band' to find the signal and also 'narrow-band' to reduce noise, leading to very different programs in different applications. For all tracking channels, the signal processing software needs the following sequence of activities:

**1. Program CHx\_CNTL register** to select the desired GPS Gold code (PRN number) for the selected satellite and code type for the mode of the correlator dithering arm – it is often best, when in acquisiton mode, to fix the dithering arm at early or at late and do a search in two phases at once and then switch to a tracking mode once a satellite is found.

2. Program CHx\_CARR\_INCR\_LO and CHx\_CARR\_INCR\_HI The values programmed into these two registers are concatenated and set the local oscillator frequency for the digital mixing performed in the GP1020 to bring the incoming 2-bit digitised signal down to baseband. The value to be programmed is equal to the nominal local oscillator frequency plus the estimated Doppler shift compensation plus the estimated user clock frequency drift compensation.

**3. Program CHx\_CODE\_INCR\_LO and CHx\_CODE\_INCR\_HI** The value to be programmed in these registers represents twice the nominal chipping rate of the C/A code (2.046 MHz) plus, if desired, a small compensation for the Doppler shift and for the user clock frequency drift.

**4. Release the tracking channel reset** by programming the RESET\_CNTL Register with the proper value. This will cause the correlation process to start.

**5. Obtain accumulated data** from Accumulated Data Register readings. Several consecutive readings on the same tracking channel can be added to increase, at will, the integration period of the correlation.

6. Decide if the GPS signal has been found by comparing the correlation result with a threshold. If found then jump to a signal pull-in algorithm. Note that both in-phase and phase quadrature accumulated data have to be considered since at this time, the carrier DCO local oscillator phase is not necessarily in phase with the incoming GPS signal.

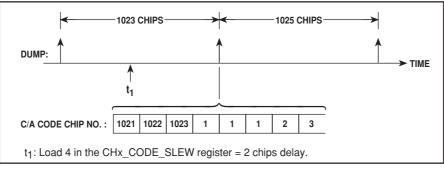

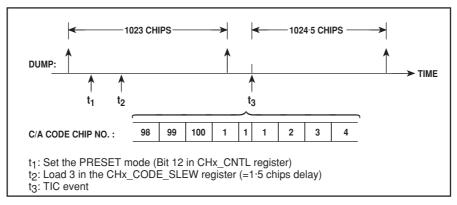

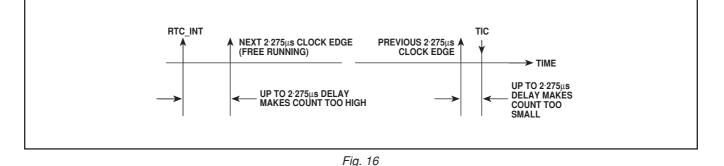

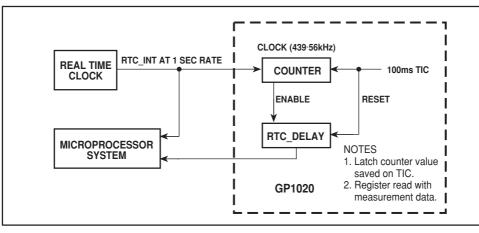

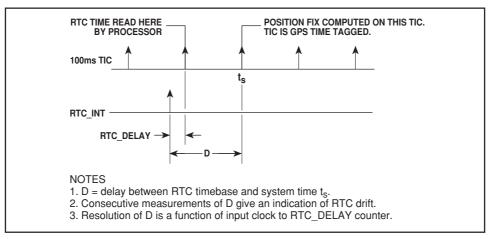

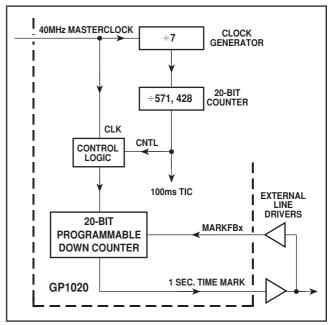

7. If the GPS signal has not been found, a new trial has to be made with different carrier DCO, code DCO, or Gold code phase programmings. Typically, both DCOs would be held constant while the Gold code phase is varied to try all of the 2046 half chip positions possible, then the carrier DCO would be programmed with slightly different values and the Gold code phase positions would again be scanned. The Gold code phase is varied by programming the CHx\_CODE\_SLEW Register and can be varied by increments of half a code chip.