# Vox Global Sourcing ICF Series

Industrial CompactFlash® Card

**Data Sheet**

**Rev. 1.0**

# **Table of contents**

| RE  | VISIO  | N HISTORY                           | 3  |

|-----|--------|-------------------------------------|----|

| LIS | T OF   | TABLES                              | 4  |

| LIS | T OF I | FIGURES                             | 5  |

| 1.  | INTE   | RODUCTION                           | 6  |

| 2.  | FEA    | TURES                               | 6  |

| 3.  | PIN    | ASSIGNMENT                          | 7  |

| 4.  | PIN    | DESCRIPTION                         | 9  |

| 5.  | SPE    | CIFICATIONS                         | 12 |

| Ę   | 5.1    | CE AND FCC COMPATIBILITY            | 12 |

| Ę   | 5.2    | ENVIRONMENTAL SPECIFICATIONS        | 12 |

|     | 5.2.   | 1 Temperature Ranges                | 12 |

|     | 5.2.2  | 2 Humidity                          | 12 |

|     | 5.2.   | 3 Shock and Vibration               | 12 |

|     | 5.2.4  | 4 Mean Time between Failures (MTBF) | 12 |

| Ę   | 5.3    | MECHANICAL DIMENSIONS               | 12 |

| Ę   | 5.4    | ELECTRICAL SPECIFICATIONS           | 13 |

|     | 5.4.   | 1 Electric Characteristic           | 13 |

|     | 5.4.2  | 2 Maximum Absolute Ratings          | 14 |

|     | 5.4.   | Recommended Operation Conditions    | 14 |

|     | 5.4.4  | 4 Timing Specifications             | 15 |

| ţ   | 5.5    | SUPPORTED IDE COMMANDS              | 16 |

| 6   | РНҮ    | SICAL OUTLINE                       | 18 |

# **REVISION HISTORY**

| Revision | Description | Date           |  |  |

|----------|-------------|----------------|--|--|

| 1.0      | Release     | September 2005 |  |  |

# **List of Tables**

| TABLE 1: ICF PIN ASSIGNMENTS                       | 7  |

|----------------------------------------------------|----|

| TABLE 2: ICF PIN DESCRIPTION                       | 9  |

| TABLE 3: SHOCK/VIBRATION TESTING FOR ICF           | 12 |

| TABLE 4: ICF MTBF                                  | 12 |

| TABLE 5: ICF ELECTRIC CHARACTERISTIC               | 13 |

| TABLE 6: ICF MAXIMUM ABSOLUTE RATINGS              | 14 |

| TABLE 7: ICF RECOMMENDED OPERATION CONDITIONS      | 14 |

| TABLE 8: READING TIMING SPECIFICATIONS, PIO MODE 4 | 15 |

| TABLE 9: WRITING TIMING SPECIFICATIONS, PIO MODE 4 | 15 |

| TABLE 10: RESET TIMING SPECIFICATIONS              | 16 |

| TARLE 11: IDE COMMANDS                             | 16 |

# **List of Figures**

| FIGURE 1: MECHANICAL DIMENSION OF ICF        | 13 |

|----------------------------------------------|----|

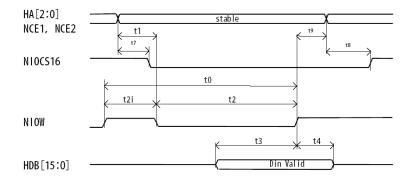

| FIGURE 2: READING TIMING DIAGRAM, PIO MODE 4 | 15 |

| FIGURE 3: WRITING TIMING DIAGRAM, PIO MODE 4 | 15 |

| FIGURE 4: RESET TIMING DIAGRAM               | 16 |

| FIGURE 5: ICF PHYSICAL OUTLINE               | 18 |

#### 1. Introduction

The IGS Industrial CompactFlash<sup>®</sup> Memory Card (ICF) products provide high capacity solid-state flash memory that electrically complies with the Personal Computer Memory Card International Association (PCMCIA) ATA (PC Card ATA) standard. (In Japan, the applicable standards group is JEIDA.) The CompactFlash<sup>®</sup> and PCMCIA cards support True IDE Mode that is electrically compatible with an IDE disk drive. The original CF form factor card can be used in any system that has a CF slot. Designed to replace traditional rotating disk drives, IGS Industrial CompactFlash<sup>®</sup> Memory Cards are embedded solid-state data storage systems for mobile computing and the industrial work place. These Industrial CompactFlash<sup>®</sup> feature an extremely lightweight, reliable, low-profile form factor.

#### 2. Features

The Industrial ATA products provide the following system features:

- Capacities: 32, 64, 128, 256, 512 and 1024MB

- PCMCIA v2.1 and PC Card v2.01 ATA compatible

- Three access mode

- Memory Card Mode

- I/O Mode

- True IDE Mode

- High reliability based on the internal ECC (Error Correction Code) function

- +3.3V/+5V single power supply operation

- Non-volatile storage (no battery required)

- Support Auto Stand-by and Sleep Mode.

- Support Master/Slave mode

- Industrial class, very rigid & rugged design

- MTBF >3,000,000 hours

- Minimum 10,000 insertions

- Shock: 30G, Vibration: 1500G

- High performance:

- Read: 10MBytes/s

- Write: 9MBytes/s

- Temperature range:

- Industrial:  $-10^{\circ}$ C  $\sim +70^{\circ}$ C

- Wide:  $-40^{\circ}$ C  $\sim +85^{\circ}$ C

- ABS Mechanical Cover

# 3. Pin Assignment

See Table 1 for ICF pin assignments.

Table 1: ICF Pin Assignments

| Pin No. | Name     | I/O   | Pull Up/Down | Schmitt Trigger | Driving Capability <sup>1</sup> |

|---------|----------|-------|--------------|-----------------|---------------------------------|

| 1       | GND      | Power |              |                 | GND                             |

| 2       | HD[3]    | I/O   |              | V               | 4 or 8 mA                       |

| 3       | HD[4]    | I/O   |              | V               | 4 or 8 mA                       |

| 4       | HD[5]    | I/O   |              | V               | 4 or 8 mA                       |

| 5       | HD[6]    | I/O   |              | V               | 4 or 8 mA                       |

| 6       | HD[7]    | I/O   |              | V               | 4 or 8 mA                       |

| 7       | CE1B     | 1     | Up           | V               |                                 |

| 8       | HA[10]   | 1     |              | V               |                                 |

| 9       | OEB      | 1     | Up           | V               |                                 |

| 10      | HA[9]    | 1     |              | V               |                                 |

| 11      | HA[8]    | I     |              | V               |                                 |

| 12      | HA[7]    | 1     |              | V               |                                 |

| 13      | HOST VCC | Power |              |                 | HOST VCC                        |

| 14      | HA[6]    | I     |              | V               |                                 |

| 15      | HA[5]    | I     |              | V               |                                 |

| 16      | HA[4]    | I     |              | V               |                                 |

| 17      | HA[3]    | I     |              | V               |                                 |

| 18      | HA[2]    | I     |              | V               |                                 |

| 19      | HA[1]    | I     |              | V               |                                 |

| 20      | HA[0]    | I     |              | V               |                                 |

| 21      | HD[0]    | I/O   |              | V               | 4 or 8 mA                       |

| 22      | HD[1]    | I/O   |              | V               | 4 or 8 mA                       |

| 23      | HD[2]    | I/O   |              | V               | 4 or 8 mA                       |

| 24      | IOIS16B  | 0     |              |                 | 4 or 8 mA                       |

| 25      | GND      | Power |              |                 | GND                             |

| 26      | GND      | Power |              |                 | GND                             |

| 27      | HD[11]   | I/O   |              | V               | 4 or 8 mA                       |

| 28      | HD[12]   | I/O   |              | V               | 4 or 8 mA                       |

| 29      | HD[13]   | I/O   |              | V               | 4 or 8 mA                       |

| 30      | HD[14]   | I/O   |              | V               | 4 or 8 mA                       |

| 31      | HD[15]   | I/O   |              | V               | 4 or 8 mA                       |

| 32      | CE2B     | I     | Up           | V               |                                 |

| 33      | VS1      | Power |              |                 | GND                             |

| 34      | IORB     | 1     | Up           | V               |                                 |

| 35      | IOWB     | 1     | Up           | V               |                                 |

| 36      | WEB      | I     | Up           | V               |                                 |

| 37      | IREQ     | 0     |              |                 | 4 or 8 mA                       |

| 38      | HOST VCC | Power |              |                 | HOST VCC                        |

| Pin No. | Name    | 1/0   | Pull Up/Down | Schmitt Trigger | Driving Capability <sup>1</sup> |

|---------|---------|-------|--------------|-----------------|---------------------------------|

| 39      | CSELB   | 1     | Up           |                 |                                 |

| 40      | VS2     | Power |              |                 | GND                             |

| 41      | RESET   | 1     | Up           | V               |                                 |

| 42      | WAITB   | 0     |              |                 | 4 mA                            |

| 43      | INPACKB | 0     |              |                 | 4 or 8 mA                       |

| 44      | REGB    | 1     | Up           | V               |                                 |

| 45      | DASPB   | I/O   | Up           | V               | 4 or 8 mA                       |

| 46      | PDIAGB  | I/O   | Up           | V               | 4 or 8 mA                       |

| 47      | HD[8]   | I/O   |              | V               | 4 or 8 mA                       |

| 48      | HD[9]   | I/O   |              | V               | 4 or 8 mA                       |

| 49      | HD[10]  | I/O   |              | V               | 4 or 8 mA                       |

| 50      | GND     | Power |              | _               | GND                             |

<sup>1.</sup> The Driving Capability "4 or 8 mA" means ---

When in 5V environment, the output driving capability is 4mA,

When in 3.3V environment, the output driving capability is 8mA, but these PAD is 5V design, so the really output capability is UNDER 8mA.

# 4. Pin Description

Table 2 describes the pin descriptions for ICF

Table 2: ICF Pin Description

| Pin No. | Pin Name                                             | I/O | Description                                                                                                                                                                                                                                                    |

|---------|------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | RESET (PC Card Memory Mode)                          | ı   | If this signal is asserted high, the card internal initialization begins to operate. During the card internal initialization RDY/BSY# is low. After the card internal initialization RDY/BSY# is high.                                                         |

| 41      | RESET<br>(PC Card I/O Mode)                          | ı   | If this signal is asserted high, the card internal initialization begins to operate. In this mode, RDY/BST# signal can not be used, so using Status Register the Ready/Busy status can be confirmed.                                                           |

|         | RESET# (True IDE Mode)                               | ı   | If this signal is asserted low, all the registers in this card are reset. In this mode, RDY/BSY# signal can not be used, so using Status Register the Ready/Busy status can be confirmed.                                                                      |

|         | CSELB<br>(PC Card Memory Mode)<br>(PC Card I/O Mode) | I   | This signal is not used.                                                                                                                                                                                                                                       |

| 39      | CSELB<br>(True IDE Mode)                             | ı   | When MSB signal is High, this signal is used to configure this device as a Master or Slave when configured in the True IDE mode. When this pin is grounded, this device is configured as a Master. When the pin is High, this device is configured as a Slave. |

| 7 22    | CE[2:1]B (PC Card Memory Mode) (PC Card I/O Mode)    | I   | CE1B and CE2B are low active card select signals. Byte/Word/Odd byte mode is defined by combination of CE1B, CE2B and HA0.                                                                                                                                     |

| 7, 32   | CE[2:1]B<br>(True IDE Mode)                          | I   | CE2B is used for select the Alternate Status Register and the Device Control Register while CE1B is the chip select for the other task file registers.                                                                                                         |

|         | REGB<br>(PC Card Memory Mode)                        | ı   | REGB is used during memory cycles to distinguish between task file and attribute memory access. High for task file, Low for attribute memory is accessed.                                                                                                      |

| 44      | REGB<br>(PC Card I/O Mode)                           | ı   | REGB is constantly low when task file or attribute memory is accessed.                                                                                                                                                                                         |

|         | REGB<br>(True IDE Mode)                              | I   | This input signal is not used and should be connected to VCC.                                                                                                                                                                                                  |

|         | OEB (PC Card Memory Mode)                            | I   | OEB is used for the control of reading register's data in attribute area or task file area.                                                                                                                                                                    |

| 9       | OEB<br>(PC Card I/O Mode)                            | I   | OEB is used for the control of reading register's data in attribute area.                                                                                                                                                                                      |

|         | ATASEL# (True IDE Mode)                              | I   | To enable True IDE mode, this input should be grounded by the host.                                                                                                                                                                                            |

|         | WEB (PC Card Memory Mode)                            | I   | WEB is used for the control of writing register's data in attribute area or task file area.                                                                                                                                                                    |

| 36      | WEB<br>(PC Card I/O Mode)                            | 1   | WEB is used for the control of writing register's data in attribute area.                                                                                                                                                                                      |

|         | WEB<br>(True IDE Mode)                               | ı   | To enable True IDE mode, this input should be connected to VCC by the host.                                                                                                                                                                                    |

| Pin No.         | Pin Name              | I/O | Description                                                                                            |  |  |  |

|-----------------|-----------------------|-----|--------------------------------------------------------------------------------------------------------|--|--|--|

|                 | IORB                  |     | This signal is not used.                                                                               |  |  |  |

|                 | (PC Card Memory Mode) | I   |                                                                                                        |  |  |  |

| 2.4             | IORB                  |     | IORB is used for control of read data in I/O task file area. This card does not                        |  |  |  |

| 34              | (PC Card I/O Mode)    | ļ   | respond to IORB until I/O card interface setting up.                                                   |  |  |  |

|                 | IORB                  |     | IORB is used for control of read data in I/O task file area. This card does not                        |  |  |  |

|                 | (True IDE Mode)       | ļ   | respond to IORB until I/O card interface setting up.                                                   |  |  |  |

|                 | IOWB                  |     | This signal is not used.                                                                               |  |  |  |

|                 | (PC Card Memory Mode) | '   |                                                                                                        |  |  |  |

| 35              | IOWB                  | 1   | IOWB is used for control of write data in I/O task file area. This card does                           |  |  |  |

| 00              | (PC Card I/O Mode)    | '   | not respond to IOWB until I/O card interface setting up.                                               |  |  |  |

|                 | IOWB                  |     | IOWB is used for control of write data in I/O task file area. This card does                           |  |  |  |

|                 | (True IDE Mode)       |     | not respond to IOWB until I/O card interface setting up.                                               |  |  |  |

|                 | HA[10:0]              |     | Address bus                                                                                            |  |  |  |

| 8, 10, 11, 12,  | (PC Card Memory Mode) | I   |                                                                                                        |  |  |  |

| 14, 15, 16, 17, | (PC Card I/O Mode)    |     |                                                                                                        |  |  |  |

| 18, 19, 20      | HA[10:0]              | 1   | Address bus. Only HA[2:0] are used.                                                                    |  |  |  |

|                 | (True IDE Mode)       |     |                                                                                                        |  |  |  |

|                 | WAITB                 |     | The WAITB signal is always driven high to signal the host to zero-delay                                |  |  |  |

|                 | (PC Card Memory Mode) | 0   | completion of a memory or I/O cycle that is in progress.                                               |  |  |  |

| 42              | (PC Card I/O Mode)    |     |                                                                                                        |  |  |  |

|                 | IORDY                 | 0   | In True IDE Mode this output signal may be used as IORDY, and always                                   |  |  |  |

|                 | (True IDE Mode)       |     | driven pull-high.                                                                                      |  |  |  |

|                 | RDY/BSY#              | 0   | The signal turns low level during the card internal initialization operation at                        |  |  |  |

|                 | (PC Card Memory Mode) |     | VCC applied or reset applied, so next access to the card should be after the signal turned high level. |  |  |  |

| 37              | IREQ                  |     | The signal of low level indicates that the card is requesting software service                         |  |  |  |

| 31              | (PC Card I/O Mode)    | 0   | to host, and high indicates that the card is not requesting.                                           |  |  |  |

|                 | INTRQ                 |     | This signal is the active high Interrupt Request to the host.                                          |  |  |  |

|                 | (True IDE Mode)       | 0   | This signal is the delive high interrupt request to the field.                                         |  |  |  |

|                 | INPACKB               |     | This signal is not used and should not be connected at the host.                                       |  |  |  |

|                 | (PC Card Memory Mode) | 0   | 1 1 3 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                |  |  |  |

|                 |                       |     | This signal is asserted low by this card when the card is selected and                                 |  |  |  |

|                 | INPACKB               |     | responding to an I/O read cycle at the address that is on the address bud                              |  |  |  |

| 43              | (PC Card I/O Mode)    | 0   | during CE# and IORD# are low. This signal is used for the input data buffer                            |  |  |  |

|                 |                       |     | control.                                                                                               |  |  |  |

|                 | INPACKB               |     | This signal is not used and should not be connected at the host.                                       |  |  |  |

|                 | (True IDE Mode)       | 0   |                                                                                                        |  |  |  |

|                 | WP                    | 0   | WP is held low because this card does not have write-protect switch.                                   |  |  |  |

|                 | (PC Card Memory Mode) |     |                                                                                                        |  |  |  |

|                 | IOIS16B               | 0   | IOIS16B is asserted (Low) when task file registers are accessed in 16-bit or                           |  |  |  |

| 24              | (PC Card I/O Mode)    |     | add byte only mode.                                                                                    |  |  |  |

|                 |                       |     | This output signal is asserted low when this device is expecting a word data                           |  |  |  |

|                 | IOIS16B               | 0   | transfer cycle. Default mode is 16-bit. The card operates in byte mode, if                             |  |  |  |

|                 | (True IDE Mode)       |     | the user issued a Set Feature Command to put the device in Byte access                                 |  |  |  |

|                 |                       |     | mode.                                                                                                  |  |  |  |

| 31, 30, 29, 28, | HD[15:0]              |     | Host data bus. HD0 is the LSB of the even byte of the word. HD8 is the LSB                             |  |  |  |

| 27, 49, 48, 47, | (PC Card Memory Mode) | I/O | of the odd byte of the word.                                                                           |  |  |  |

| 6, 5, 4, 3, 2,  | (PC Card I/O Mode)    |     |                                                                                                        |  |  |  |

| 23, 22, 21      | (True IDE Mode)       |     |                                                                                                        |  |  |  |

| Pin No. | Pin Name                      | I/O | Description                                                                                                                                                 |  |  |

|---------|-------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | BVD2<br>(PC Card Memory Mode) | I/O | BVD2 output the battery voltage status in the card. This output line is constantly driven to a high state since a battery is not required for this product. |  |  |

| 45      | SPKR# I/O (PC Card I/O Mode)  |     | SPKR# output speaker signal. This output line is constantly driven to a high state since this product does not support the audio function.                  |  |  |

|         | DASPB<br>(True IDE Mode)      | I/O | DASPB is the Slave Present signal in the Master/Slave handshake protocol. And is Disk Active signal after power on diagnostic command.                      |  |  |

|         | BVD1<br>(PC Card Memory Mode) | I/O | BVD2 output the battery voltage status in the card. This output line is constantly driven to a high state since a battery is not required for this product. |  |  |

| 46      | STSCHG# (PC Card I/O Mode)    |     | STSCHG# is used for changing the status of Configuration and Status Register in attribute area.                                                             |  |  |

|         | PDIAGB<br>(True IDE Mode)     |     | PDIAGB is the Pass Diagnostic signal in Master/Slave handshake protocol.                                                                                    |  |  |

## 5. Specifications

#### 5.1 CE and FCC Compatibility

ICF conforms to CE requirements and FCC standards.

#### 5.2 Environmental Specifications

#### 5.2.1 Temperature Ranges

Temperature Range: -10°C to +70°C

Storage Temperature: -40°C to +85°C

#### 5.2.2 Humidity

Relative Humidity: 10-95%, non-condensing

#### 5.2.3 Shock and Vibration

Table 3: Shock/Vibration Testing for ICF

| Reliability      | Test Conditions              | Reference Standards |

|------------------|------------------------------|---------------------|

| Vibration        | 7 Hz to 2 KHz, 5 g, 3 axes   | IEC 68-2-6          |

| Mechanical Shock | Duration: 10ms, 50 g, 3 axes | IEC 68-2-27         |

| Drop Unit        | From a height of 1.5 m       | IEC 68-2-32         |

#### 5.2.4 Mean Time between Failures (MTBF)

Table 5 summarizes the MTBF prediction results for various ICF configurations. The analysis was performed using a RAM Commander<sup>TM</sup> failure rate prediction.

- **Failure Rate**: The total number of failures within an item population, divided by the total number of life units expended by that population, during a particular measurement interval under stated condition.

- Mean Time between Failures (MTBF): A basic measure of reliability for repairable items: The mean number of

life units during which all parts of the item perform within their specified limits, during a particular measurement

interval under stated conditions.

Table 4: ICF MTBF

| Product Condition |                            | MTBF (Hours) | Failure Rate per Million Hours |

|-------------------|----------------------------|--------------|--------------------------------|

| ICF               | Telcordia SR-332 GB, 25 °C | 6,188,875    | 0.1616                         |

#### 5.3 Mechanical Dimensions

Mechanical Dimension: 42.80/36.40/3.30mm (W/T/H)

Ø1.60 Ø3.50 42.80

Figure 1: Mechanical Dimension of ICF

## 5.4 Electrical Specifications

## 5.4.1 Electric Characteristic

Table 5: ICF Electric Characteristic

V<sub>DD</sub>=4.5V~5.5V

|                        | 0               |      | Value    |      | 1114 | Measuring                        |

|------------------------|-----------------|------|----------|------|------|----------------------------------|

| Item                   | Symbol          | Min  | Standard | Max  | Unit | conditions                       |

| Input voltage          | V <sub>IH</sub> | 2.0  | -        | -    | V    |                                  |

| (TTL Level)            | $V_{IL}$        | -    | -        | 0.8  | V    |                                  |

| Input voltage          | V <sub>IH</sub> | 3.5  | -        | -    | V    |                                  |

| (CMOS Level)           | V <sub>IL</sub> | -    | -        | 1.5  | V    |                                  |

| Schmitt trigger        | V <sub>+</sub>  | -    | 1.51     | 2.15 | V    |                                  |

| input                  | V.              | 0.6  | 1.01     | -    | V    |                                  |

| (TTL Level)            | $V_h$           | 0.25 | -        | -    | V    |                                  |

| 0 1 1 1                | V <sub>OH</sub> | 3.7  | -        | -    | V    | I <sub>OH</sub> =2mA~-24mA       |

| Output voltage         | V <sub>OL</sub> | -    | -        | 0.4  | V    | I <sub>OL</sub> =2mA~-24mA       |

| Input leakage          | I <sub>IH</sub> | -10  | -        | 10   | μA   | V <sub>IN</sub> =V <sub>DD</sub> |

| current                | I <sub>IL</sub> | -10  | -        | 10   | μA   | V <sub>IN</sub> =GND             |

| Output leakage current | l <sub>oz</sub> | -10  | -        | 10   | μА   | Hi-Z state                       |

| Pull-up resistor       | R <sub>PU</sub> | 50   | -        | 500  | KOhm | V <sub>IN</sub> =GND             |

| Pull-down resistor     | R <sub>PD</sub> | 15.7 | -        | 128  | KOhm | V <sub>IN</sub> =V <sub>DD</sub> |

V<sub>DD</sub>=3.0V~3.6V

| ltem                   | Sumbal          | Value |          |      | Unit | Measuring                        |

|------------------------|-----------------|-------|----------|------|------|----------------------------------|

| item                   | Symbol          | Min   | Standard | Max  | Unit | conditions                       |

| Input voltage          | $V_{IH}$        | 1.75  | -        | -    | V    |                                  |

| (TTL Level)            | $V_{IL}$        | -     | -        | 0.65 | V    |                                  |

| Input voltage          | V <sub>IH</sub> | 2.15  | -        | -    | V    |                                  |

| (CMOS Level)           | V <sub>IL</sub> | -     | -        | 0.95 | V    |                                  |

| Schmitt trigger        | V <sub>+</sub>  | -     | 1.32     | 1.75 | V    |                                  |

| input                  | V.              | 0.45  | 0.86     | -    | V    |                                  |

| (TTL Level)            | $V_h$           | 0.25  | -        | -    | V    |                                  |

| 0 1 1                  | V <sub>OH</sub> | 2.4   | -        | 1    | V    | I <sub>OH</sub> =1mA~-12mA       |

| Output voltage         | $V_{OL}$        | -     | -        | 0.4  | V    | I <sub>OL</sub> =1mA~-12mA       |

| Input leakage          | I <sub>IH</sub> | -10   | -        | 10   | μA   | V <sub>IN</sub> =V <sub>DD</sub> |

| current                | I <sub>IL</sub> | -10   | -        | 10   | μA   | V <sub>IN</sub> =GND             |

| Output leakage current | l <sub>oz</sub> | -10   | -        | 10   | μА   | Hi-Z state                       |

| Pull-up resistor       | R <sub>PU</sub> | 76.6  | -        | 750  | KOhm | V <sub>IN</sub> =GND             |

| Pull-down resistor     | $R_{PD}$        | 24    | -        | 200  | KOhm | V <sub>IN</sub> =V <sub>DD</sub> |

## **5.4.2 Maximum Absolute Ratings**

Table 6: ICF Maximum Absolute Ratings

(Referenced to GND)

| Item                 | Symbol                      | Rating                      | Unit |

|----------------------|-----------------------------|-----------------------------|------|

|                      | V <sub>DD</sub> (HVCC)      | -0.6 ~ +6.0                 | V    |

| Power supply voltage | V <sub>DD</sub> (CVCC/FVCC) | -0.3 ~ +4.0                 | V    |

| Input voltage        | V <sub>IN</sub> (HVCC)      | -0.6 ~ V <sub>DD</sub> +0.6 | V    |

|                      | V <sub>IN</sub> (CVCC/FVCC) | -0.3 ~ V <sub>DD</sub> +0.3 | V    |

|                      | V <sub>IN</sub> (5V)        | -0.3 ~ +7.3                 | V    |

| Output current       | l <sub>оит</sub>            | ±15 (8mA buffer)            | mA   |

| Storage temperature  | T <sub>STG</sub>            | -55 ~ +125                  | °C   |

## **5.4.3 Recommended Operation Conditions**

**Table 7: ICF Recommended Operation Conditions**

| item                 | Symbol                                  | Rating  | Unit |

|----------------------|-----------------------------------------|---------|------|

|                      |                                         | 3.0~3.6 | V    |

| Power supply voltage | V <sub>DD</sub> (HVCC)                  | 4.5~5.5 | V    |

|                      | V <sub>DD</sub> (CVCC/FVCC)             | 3.0~3.6 | V    |

| Ambient operating    | T <sub>A</sub> (Pin Capacitance : 40pF) | -40~+85 | °C   |

| temperature          | T <sub>A</sub> (Pin Capacitance : 80pF) | 0~+70   | °C   |

Page: 14/ 18 Rev. 1.0 Data Sheet, September 2005

## 5.4.4 Timing Specifications

HA[2:0]

NCE1, NCE2

NIOCS16

t0

t2i

t2i

t5

t6

HDB[15:0]

out

Figure 2: Reading Timing Diagram, PIO Mode 4

Table 8: Reading Timing Specifications, PIO Mode 4

| Item                              | Symbol | Min (ns) | Max (ns) |

|-----------------------------------|--------|----------|----------|

| Cycle Time                        | tO     | 120      | _        |

| IORD Data Setup                   | t5     | 20       | _        |

| IORD Data Hold Time               | t6     | 5        | _        |

| IORD Data Tri-state Time          | t6Z    | _        | 30       |

| IORD Width Time                   | t2     | 70       | _        |

| IORD Recovery Time                | t2i    | 25       | _        |

| Address Setup Time                | t1     | 25       | _        |

| Address Hold Time                 | t9     | 10       | _        |

| IOIS16 Delay Falling from Address | t7     | _        | 40       |

| IOIS16 Delay Rising from Address  | t8     | _        | 30       |

Figure 3: Writing Timing Diagram, PIO Mode 4

Table 9: Writing Timing Specifications, PIO Mode 4

| Item       | Symbol | Min (ns) | Max (ns) |

|------------|--------|----------|----------|

| Cycle Time | tO     | 120      | _        |

| Item                              | Symbol | Min (ns) | Max (ns) |

|-----------------------------------|--------|----------|----------|

| IOWR Data Setup Time              | t3     | 20       | _        |

| IOWR Data Hold Time               | t4     | 10       | _        |

| IOWR Width Time                   | t2     | 70       | _        |

| Address Setup Time                | t1     | 25       | _        |

| Address Hold Time                 | t9     | 10       | _        |

| IOIS16 Delay Falling from Address | t7     | _        | 40       |

| IOIS16 Delay Rising From Address  | t8     | -        | 30       |

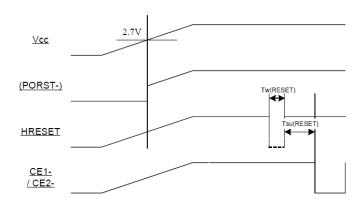

Figure 4: Reset Timing Diagram

Table 10: Reset Timing Specifications

| Item        | Symbol                  | Min | Max | Unit |

|-------------|-------------------------|-----|-----|------|

| RESET Setup | T <sub>SU</sub> (RESET) | 2   |     | ms   |

| RESET Width | T <sub>w</sub> (RESET)  | 25  |     | μS   |

## 5.5 Supported IDE Commands

ICF supports the commands listed in Table 11.

Table 11: IDE Commands

| Command Name                 | Command Code |

|------------------------------|--------------|

| CHECK POWER MODE             | 98H or E5H   |

| EXECUTE DEVICE DIAGNOSTIC    | 90H          |

| FORMAT TRACK                 | 50H          |

| IDENTIFY DEVICE              | ECH          |

| IDLE                         | 97H or E3H   |

| IDLE IMMEDIATE               | 95H or E1H   |

| INITIALIZE DEVICE PARAMETERS | 91H          |

| NOP                          | 00H          |

| READ BUFFER                  | E4H          |

Page: 16/ 18 Rev. 1.0 Data

| Command Name       | Command Code |

|--------------------|--------------|

| READ LONG SECTOR   | 22H or 23H   |

| READ MULTIPLE      | C4H          |

| READ SECTOR(S)     | 20H or 21H   |

| READ VERIFY SECTOR | 40H or 41H   |

| RECALIBRATE        | 1XH          |

| SEEK               | 7XH          |

| SET FEATURES       | EFH          |

| SET MULTIPLE MODE  | С6Н          |

| SET SLEEP MODE     | 99H or E6H   |

| STANDBY            | 96H or E2H   |

| STANDBY IMMEDIATE  | 94H or E0H   |

| WRITE BUFFER       | E8H          |

| WRITE LONG SECTOR  | E8H          |

| WRITE MULTIPLE     | C5H          |

| WRITE SECTOR(S)    | 30H or 31H   |

| WRITE VERIFY       | 3СН          |

# 6. Physical Outline

25.65 42.80 0.63 9.00 0.63 9.00 0.63 9.00 1.01 1.01

pin 26

0.99

Figure 5: ICF Physical Outline