# High Performance Bus Interface Solutions CPCI-MPSIO4

### 4-channel Serial I/O with software selectable transceivers

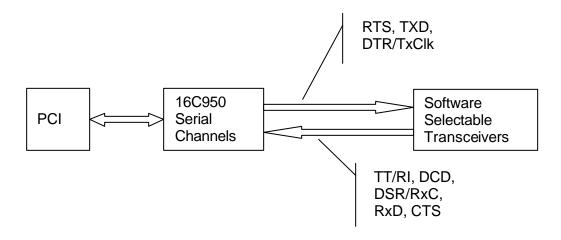

The CPCI-MPSIO4 board is a low cost 4-Channel UART with software selectable Serial I/O cable interface transceivers. Each channel can be software configured for RS-232, RS-422A, RS-449, RS-485, V.35, EIA-530, EIA-530A and V.36. The board can support up to 10 Mbits/sec for differential interfaces and 120 Kbps for single ended operation. Each transmitter and receiver has a 128 byte deep FIFO. The board is fully software compatible with 16C550 family of UARTs. The Serial I/O is through the front panel.

#### Features Include:

- Four 16C950 High performance UART channels.

- UARTs fully software compatible with 16C550 type devices.

- Asynchronous and Isochronous communications protocols.

- 128 Byte deep FIFO per Transmitter and Receiver.

- Flexible Clock Prescaler from 1 to 31.875.

- Automatic in-band flow control using programmable XON/XOFF in both directions.

- Automatic out-of-band flow control using CTS#/RTS# and/or DSR#/DTR#

- Arbitrary trigger levels for Receiver and Transmitter FIFO Interrupts.

- Global Interrupt status and readable FIFO Levels to facilitate efficient device drivers.

- Operation via IO or Memory Mapped device registers.

- Detection of bad data in the Receiver FIFO.

### Applications Include:

- ✓ LAN/WAN Networking

- ✓ Telecommunications

- ✓ Serial Interface

### High Performance Bus Interface Solutions

#### Functional Description:

The CPCI-MPSIO4 is an easy-to-use four channel full-duplex serial I/O board with software selectable transceivers. Each channel can operate up to 10 Mbits/s with a differential cable interface and 120 Kbps for single ended cable interfaces. The board is based on the Oxford Semiconductor OX16PCI954 which offers four 16C950 serial channels and the PCI interface in one space saving package. Each channel in the OX16C954 offers 128 byte deep transmitter and receiver FIFOs. The deep FIFOs reduce CPU overhead and allow higher data rates. Each channel is also software compatible with the widely used industry standard 16C550 family of devices. The board only requires simple read/write statements to operate. The UARTs are connected to the cable interface using Sipex SP504 transceivers, supporting multiple protocols in a single transceiver package.

### High Performance Bus Interface Solutions

#### ELECTRICAL SPECIFICATIONS

At +25 °C, with specified operating voltages.

#### **☐** Power Requirements

+5VDC  $\pm 0.2$  VDC at 1.5 Amps

Power Dissipation: 8.0 Watts. Worst Cast, 4 Channels Transmitting RS-485 at 10 Mbps.

6.0 Watts Typical.

#### **PCI INTERFACE**

#### **□** Compatibility:

Conforms to PCI Specification 2.2, with D32 read/write transactions.

PCI Power Management 1.0 compliant.

Supports "Plug-n-Play" initialization.

Provides a single multifunction interrupt.

#### MECHANICAL AND ENVIRONMENTAL SPECIFICATIONS

#### **☐** Physical Characteristics

Height: 7.0 mm Depth: 149.0 mm Width: 74.0 mm

#### **☐** Environmental Specifications

Ambient Temperature Range: Operating: 0 to +55 degrees Celsius

> Storage -40 to +85 degrees Celsius

Relative Humidity: Operating 0 to 80%, non-condensing

> 0 to 95%, non-condensing Storage:

Operation to 10,000 ft. Altitude:

#### **☐** Cooling Requirements

Conventional air-cooling; 200 LPFM (typical mezzanine environment).

## **High Performance Bus Interface Solutions**

#### SYSTEM I/O CONNECTIONS

The MPSIO4 offers Cable I/O through the on board cable connector. The Cable Connector pin out is listed in the following Table. The Designation \_A, \_B, \_C, and \_D Refer to the 4 serial channels on the board, channels A, B, C, and D.

Table 1 Input/Output Cable Pin Assignments

| PIN    | SIGNAL                 | PIN    | SIGNAL                 |

|--------|------------------------|--------|------------------------|

| NUMBER |                        | NUMBER |                        |

| 1      | Connector Shell Ground | 35     | Connector Shell Ground |

| 2      | Logic GND              | 36     | Logic GND              |

| 3      | RS(a)_A (-)            | 37     | RS(a)_C (-)            |

| 4      | RS(b)_A (+)            | 38     | RS(b)_C (+)            |

| 5      | SD(a)_A (-)            | 39     | SD(a)_C (-)            |

| 6      | SD(b)_ A (+)           | 40     | SD(b)_C (+)            |

| 7      | TR/TT(a)_A (-)         | 41     | TR/TT(a)_C (-)         |

| 8      | TR/TT(b)_ A (+)        | 42     | TR/TT(b)_C (+)         |

| 9      | IC/SCT(a)_A (-)        | 43     | IC/SCT(a)_C (-)        |

| 10     | IC/SCT(b)_ A (+)       | 44     | IC/SCT(b)_C (+)        |

| 11     | RR(a)_A (-)            | 45     | RR(a)_C (-)            |

| 12     | RR(b)_ A (+)           | 46     | RR(b)_C (+)            |

| 13     | DM/RT(a)_A (-)         | 47     | DM/RT(a)_C (-)         |

| 14     | DM/RT(b)_ A (+)        | 48     | DM/RT(b)_C (+)         |

| 15     | RD(a)_A (-)            | 49     | RD(a)_C (-)            |

| 16     | RD(b)_ A (+)           | 50     | RD(b)_C (+)            |

| 17     | CS(a)_A (-)            | 51     | CS(a)_C (-)            |

| 18     | CS(b)_A (+)            | 52     | CS(b)_C (+)            |

| 19     | RS(a)_B (-)            | 53     | RS(a)_D (-)            |

| 20     | RS(b)_B (+)            | 54     | RS(b)_D (+)            |

| 21     | SD(a)_B (-)            | 55     | SD(a)_D (-)            |

| 22     | SD(b)_B (+)            | 56     | SD(b)_D (+)            |

| 23     | TR/TT(a)_B (-)         | 57     | TR/TT(a)_D (-)         |

| 24     | TR/TT(b)_B (+)         | 58     | TR/TT(b)_D (+)         |

| 25     | IC/SCT(a)_B (-)        | 59     | IC/SCT(a)_D (-)        |

| 26     | IC/SCT(b)_B (+)        | 60     | IC/SCT(b)_D (+)        |

| 27     | RR(a)_B (-)            | 61     | RR(a)_D (-)            |

| 28     | RR(b)_B (+)            | 62     | RR(b)_D (+)            |

| 29     | DM/RT(a)_B (-)         | 63     | DM/RT(a)_D (-)         |

| 30     | DM/RT(b)_B (+)         | 64     | DM/RT(b)_D (+)         |

| 31     | RD(a)_B (-)            | 65     | RD(a)_D (-)            |

| 32     | RD(b)_B (+)            | 66     | RD(b)_D (+)            |

| 33     | CS(a)_B (-)            | 67     | CS(a)_D (-)            |

## **High Performance Bus Interface Solutions**

| 121 |              | 68   | CS(b) D(+)    |  |

|-----|--------------|------|---------------|--|

| 134 |              | l nx | $CS(b)_D(+)$  |  |

| J-T | (CS(U) D (1) | 00   | (CS(0), D(1)) |  |

The 68-pin DSUB (user I/O interface) connector is mounted at the front edge of the board (Reference. Designators: PA5 for row A and PB5 for row B). The part number is Amp #787170-7. The mating part number is Amp #749621-7. This cable is used for all 4 channels. Contact GSC for factory built cables of any desired length. See Table above for pin-out.

General Standards Corporation assumes no responsibility for the use of any circuits in this product. No circuit patent licenses are implied. Information included herein supersedes previously published specifications on this product and is subject to change without notice.

Email: sales@generalstandards.com