# General Standards Corporation High Performance Bus Interface Solutions

# PCI-DIO24 High-speed Parallel Digital I/O PCI Board

## Features Include:

- Data input/output width of 24 bits.

- RS422/485 differential I/O transceivers or ECL differential I/O transceivers.

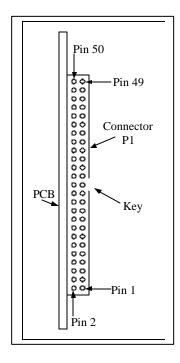

- 50 pin front panel connector for easy access via twisted pair ribbon cable.

- A single board can interface to a wide variety of external high-speed devices.

- Flexibility for custom protocols is provided by a Field Programmable Gate Array (FPGA).

- 32-Bit data transfers at 33 MHz on the PCI bus.

- 132 Mbytes per second PCI transfer rate in burst mode.

- Windows 2000 and NT drivers available with sample code.

## **Applications Include:**

- ✓ Data acquisition and control.

- ✓ General Purpose Parallel Input / Output interface.

- $\checkmark$  Development and research.

### Overview:

The DIO24 is a 24-bit discrete I/O interface board. The host side connection is PCI based and the external I/O interface is accessible through a 50 pin connector. The external interface includes 24 signals that can be arbitrarily programmed as either input or output. The 24 programmable signals are divided into three groups of eight signals each; Port A, Port B and Port C. Port A and B signals are each programmable as all inputs or all outputs. The Port C signals are individually programmable as input or output. One extra signal can be configured to generate an external clock or used as an additional input.

# General Standards Corporation High Performance Bus Interface Solutions

## **Custom Applications**

Although the DIO24 provides extensive flexibility to accommodate many user applications, custom interfaces exist which may not conform to current DIO24 interface options. General Standards Corporation has worked with many customers to provide customized versions of the DIO24 and other GSC products.

Custom protocols are implemented in an Altera FPGA. Previous custom applications implemented in FPGAs included features for counting pulses, incremental encoders, interrupt generation, special waveform generation, DMA, and many others. Modifications to existing FPGA firmware can be made by General Standards or by the customer if desired. Some other products have been implemented with Xilinx FPGAs and if necessary, a Xilinx version of the board could be developed. Please consult our sales department with your specifications to inquire about a custom application.

## RS485/422 or ECL Interface

The standard interface option utilizes RS422/485 differential I/O transceivers. A version of the PCI-DIO24 is also available with ECL differential I/O transceivers.

## **SPECIFICATIONS**

### **PCI INTERFACE**

| Compatibility: | Conforms to PCI Specification 2.1.     |  |  |  |

|----------------|----------------------------------------|--|--|--|

|                | Supports "plug-n-play" initialization. |  |  |  |

## MECHANICAL AND ENVIRONMENTAL

#### Dever Requirements

+5.0 VDC  $\pm$ 0.20 VDC at 2.0 Amps, maximum

#### **D** Physical Dimensions (Excluding panel bracket)

Height:106 mmLength:122 mm

#### □ Environmental Specifications

| Ambient Temperature Range: | Operating: 0 to +55 degrees Celsius<br>Storage: -40 to +85 degrees Celsius |

|----------------------------|----------------------------------------------------------------------------|

| Relative Humidity:         | Operating: 0 to 80%, non-condensing<br>Storage: 0 to 95%, non-condensing   |

| Altitude:                  | Operation to 10,000 ft.                                                    |

#### **Cooling Requirements**

200 LFPM minimum air flow across component side of board.

# General Standards Corporation High Performance Bus Interface Solutions

## **ORDERING INFORMATION**

The DIO24 is designed to fit a variety of high-speed digital interface needs and has several options that must be specified when being ordered. Please consult our sales department with your application requirements in order to determine the correct ordering options.

# SYSTEM I/O CONNECTIONS

| •   |              |     |                   |

|-----|--------------|-----|-------------------|

| Pin | Cable Signal | Pin | Cable Signal Name |

| No. | Name         | No. |                   |

| 1   | PORT A D0 +  | 26  | PORT B D4 -       |

| 2   | PORT A D0 -  | 27  | PORT B D5 +       |

| 3   | PORT A D1 +  | 28  | PORT B D5 -       |

| 4   | PORT A D1 -  | 29  | PORT B D6 +       |

| 5   | PORT A D2 +  | 30  | PORT B D6 -       |

| 6   | PORT A D2 -  | 31  | PORT B D7 +       |

| 7   | PORT A D3 +  | 32  | PORT B D7 -       |

| 8   | PORT A D3 -  | 33  | PORT C D0 +       |

| 9   | PORT A D4 +  | 34  | PORT C D0 -       |

| 10  | PORT A D4 -  | 35  | PORT C D1 +       |

| 11  | PORT A D5 +  | 36  | PORT C D1 -       |

| 12  | PORT A D5 -  | 37  | PORT C D2 +       |

| 13  | PORT A D6 +  | 38  | PORT C D2 -       |

| 14  | PORT A D6 -  | 39  | PORT C D3 +       |

| 15  | PORT A D7 +  | 40  | PORT C D3 -       |

| 16  | PORT A D7 -  | 41  | PORT C D4 +       |

| 17  | PORT B D0 +  | 42  | PORT C D4 -       |

| 18  | PORT B D0 -  | 43  | PORT C D5 +       |

| 19  | PORT B D1 +  | 44  | PORT C D5 -       |

| 20  | PORT B D1 -  | 45  | PORT C D6 +       |

| 21  | PORT B D2 +  | 46  | PORT C D6 -       |

| 22  | PORT B D2 -  | 47  | PORT C D7 +       |

| 23  | PORT B D3 +  | 48  | PORT C D7 -       |

| 24  | PORT B D3 -  | 49  | Dedicated INPUT   |

|     |              |     | +                 |

| 25  | PORT B D4 +  | 50  | Dedicated INPUT   |

|     |              |     | -                 |

|     |              |     |                   |

#### System Connector Pin Functions

The connector mounted on the board is manufactured by Tyco and has the part number AMP 1-103311-0. The part number of the mating connector is AMP 1-746285.

General Standards Corporation assumes no responsibility for the use of any circuits in this product. No circuit patent licenses are implied. Information included herein supersedes previously published specifications on this product and is subject to change without notice.